# Macromodels User Manual

### Preliminary

The macromodels contained in this databook operate with the Pspice and SPice simulators and with the ELDO simulator.

For most of the macromodels enclosed, no specific precautions are required for use.

They are only valid in the supply voltage and temperature conditions defined for each macromodel.

### Macromodelling

A good macromodel is a mathematical model as close as possible to the actual circuit. However, due to simulation time problems, it must be composed of simple mathematical equations.

Placed in an assembly to perform and validate an application, it must not obstruct rapid convergence of the system. Consequently, in order to satisfy requirements both for convergence speed and compliance with the actual circuit, we have considered and allowed for a certain number of important parameters.

### List of the parameters taken into consideration in the macromodels

- □ Input Offset Voltage (generally equal to "0")

- □ Input Bias Current (for bipolar input stages)

- Open-loop Gain

- Given Strequency at Unity Gain

- Gain Bandwidth

- Gain Margin

- □ Phase Margin (limited to 70°C)

- Desitive or Negative Supply Rejection Ratio

- □ Slew Rate ±

- □ Settling Time at 0.1%

- □ Input Common-mode Voltage Range

- Common-mode Rejection Ratio

- Output Impedance

- Output Current

- Supply Current

- □ Input Capacitance

#### Examples of effects not taken into consideration in the macromodels operational amplifier files

- □ The input offset voltage statistic due to the great variety in each circuit

- □ The temperature effect on the parametric values

- Input offset current

- Input noise current

- □ And some specific parameters such as distorsion, crosstalk ...

- □ Input noise voltage

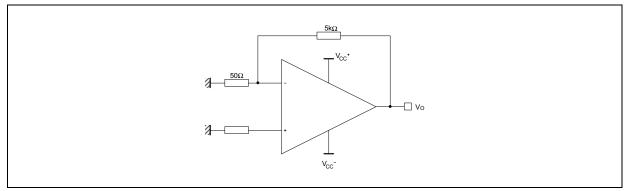

### **Operational Amplifier Macromodel File**

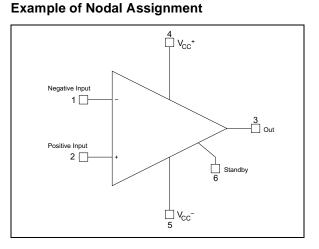

The file of an operational amplifier macromodel takes the form of a subcircuit (.subckt) followed by the name of the macromodelled circuit or the name of the original family and then by the number of the pins (1 3 2 4 5 6) with the meaning below:

- I Negative input

- □ 3 Output

- 2 Positive input

- $\Box$  4 V<sub>CC</sub><sup>+</sup> Positive supply

- $\Box$  5 V<sub>cc</sub> Negative supply

- □ 6 Standby input (for specific circuit)

Further to this, we find the list of elementary components making up the macromodel.

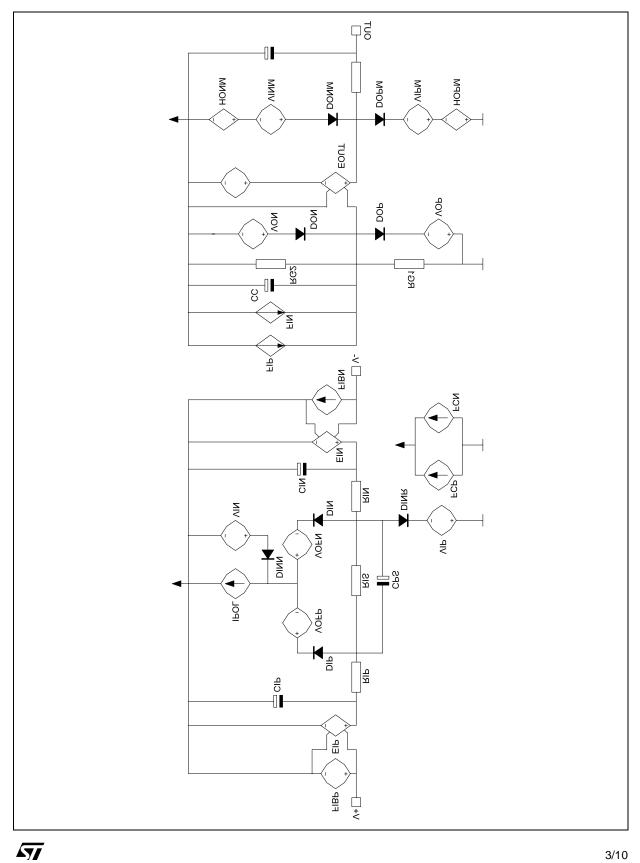

Example: \* Input Stage CIP 2 5 1.0 E-12 CIN 1 5 1.0 E-12 ... etc... cf TS902 macromodel table

Followed or preceded by simple component models such as diodes and transistors.

**Example:** . model MDTH D Is = 1E-8 KF = 6,657412e+01 ...

### Macromodel Component

Prefix Definition

| Prefix | Definition                           |  |

|--------|--------------------------------------|--|

| С      | Capacitor                            |  |

| d      | Diode                                |  |

| е      | Voltage controlled by voltage source |  |

| f      | Current controlled by current source |  |

| g      | Voltage controlled by current source |  |

| h      | Current controlled by voltage source |  |

| r      | Resistor                             |  |

| V      | Independent voltage source           |  |

| I      | Independent current source           |  |

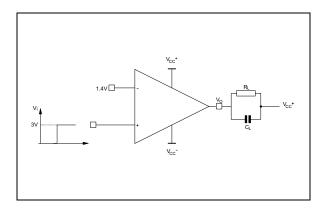

# Schematic Example

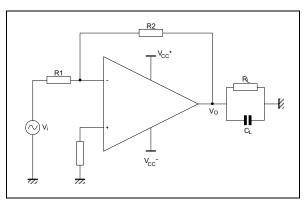

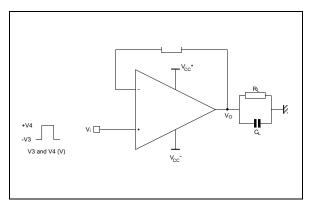

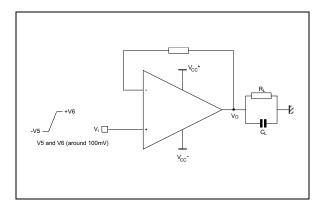

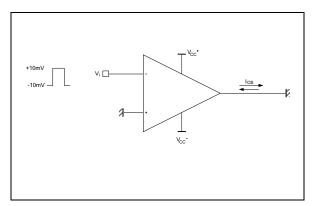

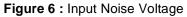

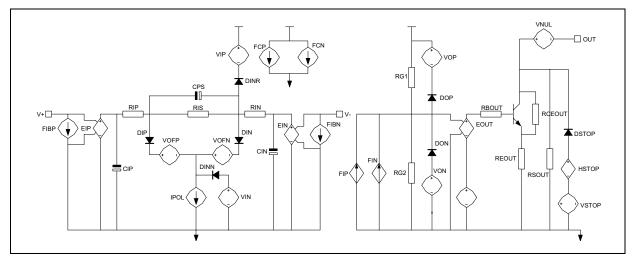

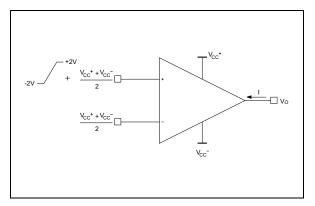

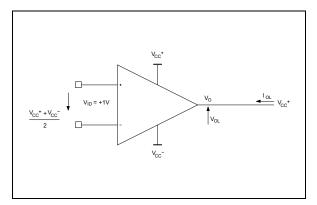

To check the relative accuracy of the subcircuit compared to the real operational amplifier we have used the circuit configuration as you can see on the following figures.

Figure 1 : Gain on Phase versus Frequency

Figure 2 : Transfer Function and DC Output

Figure 3 : Slew Rate

Figure 4 : Overshoot

Figure 5 :  $I_{os}^+ / I_{os}^-$  - Dual Supply

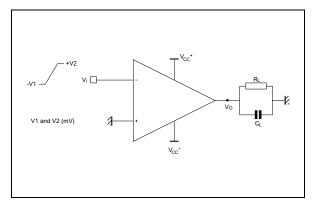

# Figure 5 bis : Single Supply

# Example: TS902

# **ELECTRICAL CHARACTERISTICS**

$V_{CC}^{+}$  = 5V,  $V_{CC}^{-}$  = 0V,  $R_L$ ,  $C_L$  connected to  $V_{CC/2}$ , Standby OFF,  $T_{amb}$  = 25°C (unless otherwise specified)

| Symbol               | Conditions                        | Value       | Unit    |

|----------------------|-----------------------------------|-------------|---------|

| V <sub>io</sub>      |                                   | 0           | mV      |

| A <sub>vd</sub>      | $R_{L} = 10k\Omega$               | 30          | V/mV    |

| I <sub>CC</sub>      | No load, per operator             | 230         | μΑ      |

| V <sub>icm</sub>     |                                   | -0.2 to 5.2 | V       |

| V <sub>OH</sub>      | $R_L = 10k\Omega$                 | 4.95        | V       |

| V <sub>OL</sub>      | $R_L = 10k\Omega$                 | 50          | mV      |

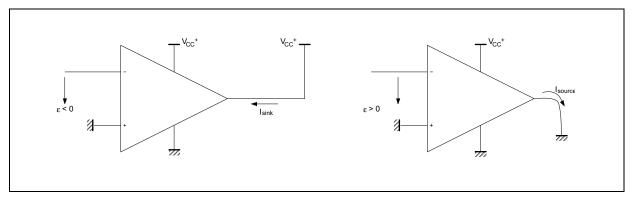

| I <sub>sink</sub>    | $V_0 = 10V$                       | 60          | mA      |

| Isource              | $V_0 = 0V$                        | 60          | mA      |

| GBP                  | $R_L = 10k\Omega$ , $C_L = 100pF$ | 0.8         | MHz     |

| SR                   | $R_L = 10k\Omega, C_L = 100pF$    | 0.8         | V/µs    |

| φm                   | $R_L = 10k\Omega$ , $C_L = 100pF$ | 30          | Degrees |

| I <sub>CC STBY</sub> | V <sub>STBY</sub> = 0V            | 500         | nA      |

The macromodel file must end with

.ENDS

For each macromodel we give a table in which we define the conditions in which the models have been validated as well as the main validation results.

# **Comparator Macromodel File**

The file of a comparator macromodel takes the form of a subcircuit (.subckt) followed by the name of the macromodelled circuit or the name of the original family.

This is followed by the number of the pins (1 3 2 4 5) with the meaning below :

- I Negative Input

- 3 Output

- 2 Positive Input

- $\Box$  4 V<sub>CC</sub><sup>+</sup> Positive supply

- $\Box$  5 V<sub>cc</sub><sup>-</sup> Negative supply

Further to this, we find the list of elementary components making up the macromodel.

**Example:** \* Input Stage

CIP 2 5 1.0 E-12

### Schematic Example

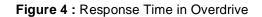

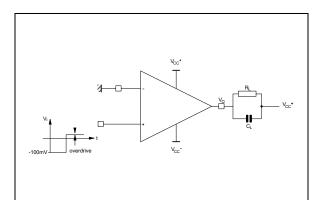

To check the relative accuracy of the subcircuit compared to the real comparator we have used the circuit configuration as you can see in the following figures.

Figure 1 : Input Bias and Supply Current

Figure 2 : Maximum I<sub>SINK</sub> Current and I<sub>SOURCE</sub> Current when the Output is at a High Level

Figure 3 : Low Level Output Voltage

Figure 4 bis : Response Time in TTL

# GLOSSARY

# INPUT BIAS CURRENT

The difference between input and output currents.

Note: This is sometimes referred to as quiescent current.

# COMMON-MODE INPUT VOLTAGE: (V<sub>ic</sub>)

The average of the two input voltage.

# COMMON-MODE INPUT VOLTAGE RANGE: (Vicm)

The range of the common-mode input voltage where the amplifier works as well as possible.

# COMMON-MODE REJECTION RATIO: (CMR)

The ratio of differential amplification to common-mode voltage amplification.

Note: this is measured by determining the ratio of the specified range of input common-mode voltage to the variation of the input offset voltage.

# DIFFERENTIAL INPUT RESISTANCE: (r<sub>id</sub>)

The small-signal resistance between the two ungrounded input terminals.

# **CROSSTALK ALTERATION: (V01/V02)**

The ratio of the change in output voltage of a driver channel to the resulting change in output voltage of another channel.

# DIFFERENTIAL INPUT VOLTAGE: (V<sub>id</sub>)

The difference of the voltage between the non-inverting input and the inverting input.

# DIFFERENTIAL INPUT VOLTAGE RANGE: (Vid)

The range of voltage between the two input terminals than we can put without damage for the circuit.

# DIFFERENTIAL VOLTAGE AMPLIFICATION: (Avd)

The ratio of the change in output voltage to the change in differential input voltage producing it.

### **DYNAMIC IMPEDANCE: (ZKA)**

The quotient of a change in voltage across the voltage reference and the corresponding change in current through the voltage reference when it is biased for regulation.

### EQUIVALENT INPUT NOISE CURRENT: (In)

The current of an ideal current source (having an internal impedance equal to zero) in series with the input terminals of the circuit that represents the part of the internally generated noise that can properly be represented by a current source.

# EQUIVALENT INPUT NOISE VOLTAGE: ( $e_n$ )

The voltage of an ideal voltage source (having an internal impedance equal to zero) in series with the input terminals of the circuit that represents the part of the internally generated noise that can properly be represented by a voltage source).

### GAIN MARGIN: (A<sub>m</sub>)

The reciprocal of the open-loop voltage amplification at the lowest frequency at which the open-loop phase shift is such that the output is in phase with the inverting-input.

# HIGH LEVEL OUTPUT CURRENT: ( $I_{OH}$ )

The current into an output with input condition applied that, according to the product specification, will establish a high level at the output.

# HIGH LEVEL OUTPUT VOLTAGE: (V<sub>OH</sub>)

The voltage at an output with input condition applied that according to the product specification will establish a high level at the output.

# INPUT BIAS CURRENT: (I<sub>ib</sub>)

The average of the currents into the two input terminals with the output at 0V.

### INPUT CAPACITANCE: (C<sub>i</sub>)

The capacitance between the input terminals with either input grounded.

# INPUT OFFSET CURRENT: (I<sub>io</sub>)

The difference between the currents into the two input terminals with the output at 0V.

# INPUT OFFSET VOLTAGE: (V<sub>io</sub>)

the DC voltage that must be applied between the input terminals to force the quiescent DC output voltage to zero or other level, if specified.

### INPUT RESISTANCE: (r<sub>i</sub>)

The resistance between the input terminals with either input grounded.

### INPUT VOLTAGE RANGE: (Vi)

The range of voltage than we can apply to the input without damaging for the device.

### LARGE SIGNAL VOLTAGE AMPLIFICATION: (A<sub>V</sub>)

The ratio of the peak to peak output voltage surving to the change in input voltage required to drive the output.

### LOW LEVEL OUTPUT CURRENT: (I<sub>OL</sub>)

The current into an output with input conditions applied that according to the product specification will establish a low level at the output.

### MAXIMUM PEAK TO PEAK OUTPUT VOLTAGE SWING: (V<sub>OPP</sub>)

The maximum peak to peak output voltage that can be obtained without waveform clipping when the quiescent DC output voltage is zero.

### **OUTPUT IMPEDANCE: (Z<sub>o</sub>)**

The small signal impedance between the output terminal and ground.

### OUTPUT RESISTANCE: $(r_{o})$

The resistance between the output terminal and ground.

###

The absolute value of the open-loop phase shift between the output and the inverting input at the frequency at which the modulus of the open-loop amplification is unity.

### **RESPONSE TIME**

The interval between the application of an input step function and the instant the output crosses the logic threshold voltage.

### RISE TIME: (t<sub>r</sub>)

The time required for an output voltage step to change from 10% to 90% of its final value.

### SHORT-CIRCUIT OUTPUT CURRENT: (Ios)

The maximum output current available from the amplifier with the output shorted to ground, to either supply, or to specified point.

# SLEW-RATE: (SR)

The average time rate of change of the closed-loop amplifier output voltage for a step signal input.

# STANDBY CURRENT: (I<sub>stb</sub>)

The current flowing through the standby terminal when it is on.

### SUPPLY CURRENT : (I<sub>CC</sub>)

The current into the  $V_{cc}^+$  or  $V_{cc}^-$  terminal of our integrated circuit.

# SUPPLY VOLTAGE REJECTION RATIO: (SVR) ( $\Delta V_{cc}$ / $\Delta V_{io}$ )

The absolute value of the ratio of the change in supply voltage ot the change in input offset voltage.

### TOTAL POWER DISSIPATION: (P<sub>D</sub>)

The total DC power supplied to the device less any power delivered from the device to a load.

# SETTLING TIME

The time between a step function change of the input signal level and the instant at which the magnitude of the output signal reaches for the last time a specified level range ( $\pm \Sigma$ ) containing the final output signal level.

### UNITY GAIN BANDWIDTH

The range of frequencies within which the open-loop voltage amplification is operated than unity.

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

© The ST logo is a registered trademark of STMicroelectronics

© 2002 STMicroelectronics - Printed in Italy - All Rights Reserved STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States

© http://www.st.com