June 25, 2010

# C8051F990/1/6/7, C8051F980/1/2/3/5/6/7/8/9 Rev. A/B Errata

## **Errata Status Summary**

| Errata # | Title                                                    | Status                              |                                     |

|----------|----------------------------------------------------------|-------------------------------------|-------------------------------------|

|          |                                                          | Rev A Device                        | Rev B Device                        |

| 1        | Capacitive sense pin monitor                             | See Errata Details 1                | Fixed                               |

| 2        | CS0MD1 bit mapping                                       | See Errata Details 2                | Fixed                               |

| 3        | No ADC Input on P1.4                                     | See Errata Details 3                | Fixed                               |

| 4        | SmaRTClock startup time                                  | See Errata Details 4                | Fixed                               |

| 5        | Non Sleep Mode Current                                   | See Errata Details 5                | Fixed                               |

| 6        | Writes to CRC0CN that initiate a CRC0 operation          | See Errata Details 6                | Fixed                               |

| 7        | Address 0x0000 of XRAM                                   | Information<br>See Errata Details 7 | Information<br>See Errata Details 7 |

| 8        | POR Supply Monitor for supply voltages greater than 2.4V | Information<br>See Errata Details 8 | Information<br>See Errata Details 8 |

Rev B is recommended for production.

## **Errata Details**

#### 1. Capacitive Sense Pin Monitor

**Description**: An issue has been identified with the capacitive sense pin monitor function when the device enters Suspend mode. If the pin monitor is enabled, under some circumstances, conversions may be continuously initiated.

Impacts: The Capacitive sense conversion may not complete due to continuously being restarted.

Workaround: Disable all pin monitor functionality (CS0PM = 0x00) before entering Suspend mode.

**Resolution**: Fixed in Rev B and later.

#### 2. CS0MD1 Bit Mapping

**Description**: Bit 4 and Bit 5 of CS0MD1 have been incorrectly mapped to Bit 5 and Bit 6.

**Impacts**: Both the CS0 Digital Polarity Select and the CS0 Double Reset Select function share the same bit (Bit 5) in the CS0MD1 register. This may cause a limitation in functionality if these functions are being used.

**Workaround**: Since making a change to one of the functions will cause a change to the other function, care should be taken when setting up either function. If Bit 5 and Bit 6 are not written, then the device will follow the default behavior described in the data sheet.

**Resolution**: Fixed in Rev B and later.

#### 3. No ADC Input on P1.4

Description: An issue has been identified that prevents P1.4 from being routed to the ADC.

**Impacts**: On C8051F996/7/8/9 devices, P1.4 cannot be used as an analog input for the ADC. This behavior does not affect C8051F990/1/2/3/4/5 devices.

**Resolution**: Fixed in Rev B and later.

#### 4. SmaRTClock Startup Time

**Description**: A modification was made to the SmaRTClock crystal driver circuit.

**Impacts**: The startup time of the SmaRTClock crystal oscillator is longer than other devices in the 'F9xx family. Instability may occur at voltages above 3.0 V. The "Oscillator Robustness Test" described in the data sheet is not a valid way to determine oscillator robustness for this silicon revision.

**Workaround**: Disable automatic gain control or use bias doubling to increase the drive current if the crystal has high ESR (> 40 k $\Omega$ ) or if the supply voltage is greater than 3.0 V.

**Resolution**: Fixed in Rev B and later.

#### 5. Non Sleep Mode Current

**Description**: An internal pull-up transistor is enabled, drawing approximately 100  $\mu$ A, when the precision oscillator is disabled.

**Impacts**: In all power modes other than Sleep mode, device power consumption will be 100  $\mu$ A higher than data sheet specifications if the precision oscillator is disabled.

Resolution: Fixed in Rev B and later.

400 West Cesar Chavez, Austin, TX 78701 www.silabs.com

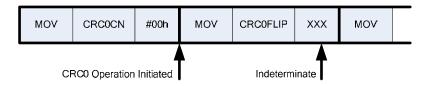

#### 6. Writes to CRC0CN that Initiate a CRC0 Operation

**Description**: The third op-code byte fetched from program memory following a write to CRC0CN that initiates a CRC0 operation is indeterminate.

**Impacts**: If the indeterminate op-code byte is the first or second byte in an instruction, improper code execution may result.

**Workaround**: Writes to CRC0CN that initiate a CRC0 operation must be immediately followed by a benign 3byte instruction whose third byte is a "don't care." An example of such an instruction is the write of a dummy value to the CRC0FLIP register using a 3-byte MOV instruction. The value written to CRC0FLIP will be indeterminate, but this should have no effect on the system. To ensure that both instructions are executed without interruption, global interrupts should be disabled.

**Note**: When programming in C, the dummy value written to CRC0FLIP should be a non-zero value. This prevents the compiler from generating the following instruction sequence:

CLR A MOV CRC0FLIP, A

When programming in C, the disassembly should be checked to ensure the compiler generated the following instruction sequence:

MOV CRC0FLIP, #AAh where #AAh is the non-zero dummy value.

**Resolution**: Fixed in Rev B and later.

#### 7. Address 0x0000 of XRAM

**Description**: On device reset, or upon waking up from Sleep mode, address 0x0000 of external memory may be overwritten by an indeterminate value. The indeterminate value is 0x00 in most situations.

**Impacts**: Application data stored at 0x0000 in external memory may be overwritten upon reset or waking up from sleep mode.

**Workaround**: A dummy variable should be placed at address 0x0000 in external memory to ensure that the application software does not store any data that needs to be retained during sleep or reset at this memory location. The compiler-independent example below shows how to locate a dummy variable at address 0x0000 in external memory.

LOCATED\_VARIABLE\_NO\_INIT (reserved, U8, SEG\_XDATA, 0x0000);

Compiler-independent code requires the use of the compiler\_defs.h and c8051F990\_defs.h header files supplied in the C:\Silabs\MCU\INC folder after installation of the Silicon Laboratories IDE.

Resolution: This information will be added to the device data sheet.

### 8. POR Supply Monitor for supply voltages greater than 2.4 V

**Description**: The POR Supply Monitor should not be disabled if the supply voltage is greater than 2.4 V.

**Impacts**: The lowest power sleep mode current, 10 nA typical, can only be achieved when the supply voltage is less than 2.4 V. The lowest power sleep mode for voltages above 2.4 V is 50 nA typical, with the POR Supply Monitor enabled.

**Resolution**: This information will be added to the device data sheet.

#### Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products must not be used within any Life Support System without the specific to result in significant personal injury or death. Silicon Laboratories products are generally not intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products are generally not intended for military applications. Silicon Laboratories products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**

Silicon Laboratories Inc., Silicon Laboratories, Silicon Labs, SiLabs and the Silicon Labs logo, CMEMS®, EFM, EFM32, EFR, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZMac®, EZRadio®, EZRadioPRO®, DSPLL®, ISOmodem ®, Precision32®, ProSLIC®, SiPHY®, USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA

### http://www.silabs.com