### High Performance RGB Driver for DLP/LCD/LCoS Projectors

#### Features

- Three 2A common anode LED/laser drivers

- Integrated 12.5 Msps 10-bit current DACs with 6-bit programmable full scale

- · Real-time continuous and integrating optical power control

- · DC-DC control circuitry

- Safety circuitry

- High speed 4 wire interface or I<sup>2</sup>C

#### **Applications**

- DLP/LCD/LCoS Projector Systems

- Backlight illumination

The M08888 is a high efficiency integrated triple channel 2A LED/laser driver for LCD/LCoS/DLP projection displays. It features automatic optical power control for consistent white balance across temperature variation and light source aging. The M08888 allows for the control of an external DC-DC converter to generate optimal light sources supply and improve overall system efficiency. An internal junction temperature monitor is also available. The part can be programmed via I<sup>2</sup>C or high speed 4-wire SPI interface.

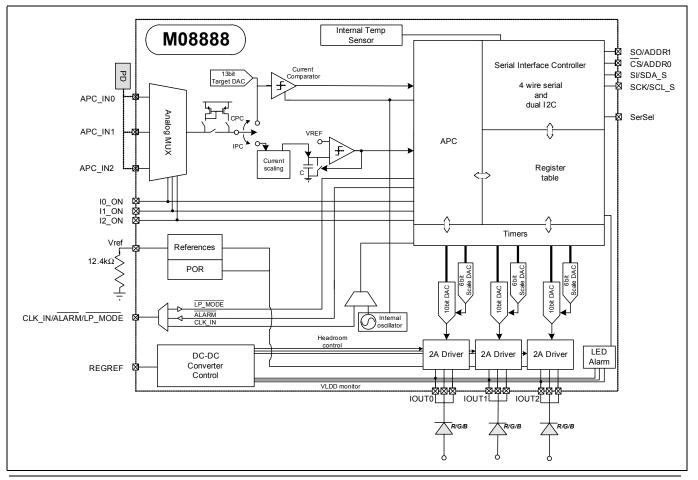

#### M08888 Block Diagram

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

1

Rev V4

MACOM

### High Performance RGB Driver for DLP/LCD/LCoS Projectors

### **Ordering Information**

| Part Number                                                                                 | Package                         | Operating Temperature |  |  |  |

|---------------------------------------------------------------------------------------------|---------------------------------|-----------------------|--|--|--|

| M08888G-11 *                                                                                | 28 pin, 4.5 mm x 4.5 mm QFN     | -40 °C to +85 °C      |  |  |  |

| M08888-11EVM                                                                                | Evaluation board with M08888-11 | -40 °C to +85 °C      |  |  |  |

| * The letter "G" designator in the part number indicates that the device is RoHS-compliant. |                                 |                       |  |  |  |

### **Revision History**

| Revision | Level       | Date           | Description                                                                                                                                            |

|----------|-------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| V4       | Release     | July 2015      | Updated register references.                                                                                                                           |

| E (V3)   | Release     | September 2011 | Updated Ordering Information                                                                                                                           |

| D (V2)   | Release     | August 2011    | Add operating specifications at Tc=120°C in Tables 1-5, 1-6 and 1-8. Change pin24 from DIS to GND.                                                     |

| C (V1)   | Release     | June 2011      | Update Product Specifications, Functional Descriptions and Register Descriptions                                                                       |

| B (V1P)  | Preliminary | October 2010   | Update Product Specifications, Functional Description and Register Descriptions.<br>Swapped pinout of <i>ADDR0</i> (pin 19) and <i>ADDR1</i> (pin 18). |

| A (V1A)  | Advance     | June 2010      | Initial                                                                                                                                                |

### Conventions

Throughout this document, pins will be identified with italics (example *IOUT1*) while x or X means 0,1,2 to indicate the different channels.

# **1.0 Product Specification**

## 1.1 Absolute Maximum Ratings

These are the absolute maximum ratings at or beyond which the IC can be expected to fail or be damaged. Reliable operation at these extremes for any length of time is not implied.

| Symbol                                                             | Parameter                                               | Rating                          | Units |

|--------------------------------------------------------------------|---------------------------------------------------------|---------------------------------|-------|

| DV <sub>DD</sub> , ALV <sub>DD</sub>                               | 1.8 V Digital and Analog Voltage at pins DVDD and ALVDD | 1.98                            | V     |

| DHV <sub>DD,</sub> AHV <sub>DD</sub>                               | 3.3 V Digital and Analog Voltage at pins DVDD and ALVDD | 3.63                            | V     |

| IOUT0, IOUT1, IOUT2                                                | Output pins for driving LED/Laser - maximum voltage     | 5.5                             | V     |

| T <sub>JCTN</sub>                                                  | Junction Temperature                                    | -40 to +125                     | °C    |

| T <sub>STG</sub>                                                   | Storage Temperature                                     | -65 to +150                     | °C    |

| SERSEL                                                             | Serial data format select input                         | -0.4 to 3.63                    | V     |

| APC_IN0, APC_IN1, APC_IN2                                          | RGB Photodiode Feedback Input Voltage                   | -0.4 to ALV <sub>DD</sub> + 0.4 | V     |

| I <sub>APC_IN0</sub> , I <sub>APC_IN1</sub> , I <sub>APC_IN2</sub> | RGB Photodiode Feedback Input Current                   | -0.5 to 4                       | mA    |

| I_VREF                                                             | Current into Reference Voltage Pin                      | -0.12 to +0.12                  | mA    |

| 10_ON, 11_ON, 12_ON                                                | Enable LED/Laser output                                 | -0.4 to 3.63                    | V     |

| CLK_IN, CS, SI, SCLK, SO                                           | SPI inputs and output                                   | -0.4 to 3.63                    | V     |

| SCLK_S, SDA_S                                                      | I <sup>2</sup> C interface                              | -0.4 to 3.63                    | V     |

| REGREF                                                             | External DC-DC converter control signal                 | -0.4 to DV <sub>DD</sub> +0.4   | V     |

| I_REGREF                                                           | Current into or out of REGREF                           | -0.12 to +0.12                  | mA    |

Table 1-1. Absolute Maximum Ratings

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

Rev V4

## 1.2 DC Characteristics

Min and Max values: Tc= -40 °C to 85 °C,  $DV_{DD}$ =1.8 V+/-5%,  $ALV_{DD}$ =1.8 V+/-5%,  $DHV_{DD}$ =3.3 V+/-5%,  $AHV_{DD}$ =3.3 V+/-5% unless otherwise noted. Typical values: Tc=25 °C,  $DV_{DD}$ =1.8 V,  $ALV_{DD}$ =1.8 V,  $DHV_{DD}$ =3.3 V,  $AHV_{DD}$ =3.3 V unless otherwise noted.

| Symbol            | PARAMETER                                              | CONDITIONS                                        | Min  | Тур  | Max  | Units |

|-------------------|--------------------------------------------------------|---------------------------------------------------|------|------|------|-------|

| DV <sub>DD</sub>  | 1.8 V supply for digital circuitry                     |                                                   | 1.71 | 1.8  | 1.89 | V     |

| ALV <sub>DD</sub> | 1.8 V supply for analog circuitry                      |                                                   | 1.71 | 1.8  | 1.89 | V     |

| DHV <sub>DD</sub> | 3.3 V supply for digital circuitry                     |                                                   | 3.13 | 3.3  | 3.47 | V     |

| AHV <sub>DD</sub> | 3.3 V supply for analog circuitry                      |                                                   | 3.13 | 3.3  | 3.47 | V     |

| I <sub>LVDD</sub> | 1.8 V Supply Current                                   | Open Loop                                         | _    | 18.5 | 21.5 | mA    |

|                   | $(DV_{DD} and ALV_{DD})^{1, 2}$                        | Closed Loop (IPC)                                 | —    | 8.5  | 11   |       |

|                   |                                                        | Closed Loop (CPC)                                 | —    | 22   | 30   |       |

| I <sub>HVDD</sub> | 3.3 V (DHV <sub>DD</sub> and $AHV_{DD}$ ) <sup>1</sup> | Open Loop                                         | —    | 7.5  | 13   | mA    |

|                   | Standby Current - 3.3 V                                | Closed Loop (IPC) additional to open loop current | —    | -    | 0.05 |       |

|                   |                                                        | Closed Loop (CPC)                                 | -    | 2.5  | 3.2  |       |

| LV <sub>POR</sub> | 1.8 V SET Threshold                                    | For positive going supply                         | _    | 1.5  | _    | V     |

|                   | 1.8 V RESET Threshold                                  | For negative going supply                         |      | 1.4  |      |       |

| HV <sub>POR</sub> | 3.3 V SET Threshold                                    | For positive going supply                         | _    | 2.72 | —    | V     |

|                   | 3.3 V RESET Threshold                                  | For negative going supply                         |      | 2.62 |      |       |

| Тс                | Case Temp.                                             | Measured on top of M08888 case                    | -40  | -    | 85   | °C    |

#### Table 1-2. DC Characteristics

NOTES:

1. Excludes serial interface (SPI/I<sup>2</sup>C) current and LED current

2. I<sub>LVDD</sub> will be increase by 0.5% of the *Ix\_OUT* current when *Ix\_OUT* is active. For the specified values inputs are toggling at 1 kHz at 50% of maximum *Ix\_OUT* current.

## 1.3 APC Input Characteristics (register 4Ah[4]=1b)

**Min and Max values:** Tc= -40 °C to 85 °C, DV<sub>DD</sub>=1.8 V+/-5%, ALV<sub>DD</sub>=1.8 V+/-5%, DHV<sub>DD</sub>=3.3 V+/-5%, AHV<sub>DD</sub>=3.3 V+/-5% unless otherwise noted. **Typical values:** Tc=25 °C, DV<sub>DD</sub>, ALV<sub>DD</sub>=1.8 V, AHV<sub>DD</sub>=3.3 V

Table 1-3.

APC Input Characteristics (photodiode cathode connected to pin APC\_INX and photodiode anode connected to ground)

| Parameter                   | Conditions                                                                                                                      | Minimum | Typical | Maximum | Units |  |  |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|-------|--|--|

| Full scale input            | APC_IN0,1,2                                                                                                                     | 3.1     | 3.25    | 3.4     | mA    |  |  |

| PD capacitance <sup>1</sup> | APC_IN0,1,2                                                                                                                     | -       | -       | 80      | pF    |  |  |

| Input bias                  | APC_IN0,1,2                                                                                                                     | -       | 1.8     | —       | V     |  |  |

| Maximum input voltage       |                                                                                                                                 | -       | _       | 1.89    | V     |  |  |

| NOTES:                      |                                                                                                                                 |         |         |         |       |  |  |

| 1. Care should be taken     | . Care should be taken in routing of each PD input so that total capacitance on the pin including routing does not exceed 80 pF |         |         |         |       |  |  |

## 1.4 APC Input Characteristics (register 4Ah[4]=0b)

Min and Max values: Tc= -40 °C to 85 °C,  $DV_{DD}$ =1.8 V+/-5%,  $ALV_{DD}$ =1.8 V+/-5%,  $DHV_{DD}$ =3.3 V+/-5%,  $AHV_{DD}$ =3.3 V+/-5% unless otherwise noted. Typical values: Tc=25 °C,  $DV_{DD}$ ,  $ALV_{DD}$ =1.8 V,  $AHV_{DD}$ =3.3 V

Table 1-4. APC Input Characteristics (Current Sink Input)

| Parameter                   | Conditions               | Minimum | Typical | Maximum | Units |

|-----------------------------|--------------------------|---------|---------|---------|-------|

| Full scale input            | APC_IN0,1,2 <sup>2</sup> | 3.1     | 3.25    | 3.4     | mA    |

| PD capacitance <sup>1</sup> | APC_IN0,1,2 <sup>2</sup> | _       | _       | 300     | pF    |

| Min Input bias              | APC_IN0,1,2 <sup>2</sup> | _       | 0.6     |         | V     |

| Maximum input voltage       |                          | —       | _       | 1.89    | V     |

NOTES:

1. Care should be taken in routing of each PD input so that total capacitance on the pin including routing does not exceed 300 pF

2. Only a single channel can be used (broadband monitor photodetector). If multiple channel are used accuracy is not guaranteed.

#### **CPC Target DAC** 1.5

Min and Max values: Tc= -40 °C to 85 °C,  $DV_{DD}$ =1.8 V+/-5%,  $ALV_{DD}$ =1.8 V+/-5%,  $DHV_{DD}$ =3.3 V+/-5%, AHV<sub>DD</sub> =3.3 V+/-5% unless otherwise noted. Typical values: Tc=25 °C, DV<sub>DD</sub>, ALV<sub>DD</sub>=1.8 V, AHV<sub>DD</sub> =3.3 V

| Table 1-5. | CPC Target DAC  |

|------------|-----------------|

|            | or o rarger DAO |

| Parameter                                | Conditions        | Minimum | Typical | Maximum | Units |

|------------------------------------------|-------------------|---------|---------|---------|-------|

| Resolution                               |                   | —       | 13      | —       | bits  |

| Conversion rate                          |                   | —       | 30      | —       | Msps  |

| Full scale monitor photodetector current |                   | _       | 3.25    | 3.4     | mA    |

| Step size                                |                   | —       | 350     | 515     | nA    |

| CPC Control Loop Accuracy <sup>1</sup>   |                   | -6      | —       | 6       | %     |

| NOTES:<br>1. At Tc= 120 °C control loop  | accuracy is +/-7% |         |         |         |       |

#### 1.6 Integrating Power Control

Min and Max values: Tc= -40 °C to 85 °C, DV<sub>DD</sub>=1.8 V+/-5%, ALV<sub>DD</sub>=1.8 V+/-5%, DHV<sub>DD</sub>=3.3 V+/-5%, AHV<sub>DD</sub> =3.3 V+/-5% unless otherwise noted. Typical values: Tc=25 °C, DV<sub>DD</sub>, ALV<sub>DD</sub>=1.8 V, AHV<sub>DD</sub> =3.3 V

Table 1-6. Integrating Power Control

| Parameter              | Conditions                                 | Minimum | Typical | Maximum | Units |

|------------------------|--------------------------------------------|---------|---------|---------|-------|

| Resolution             |                                            | _       | 10      | _       | bits  |

| Count variation        | Part to part                               | -35     |         | +35     | %     |

| Stability <sup>2</sup> | For targets > 200 µA and register 0x0B=50h | -11     | _       | +11     | %     |

| NOTES                  |                                            |         |         |         |       |

This will correspond to a total power (LED/MPD current?) variation: monotonicity will still be guaranteed by the architecture 1.

2. Variation of integration target over supply and temperature. At Tc= 120 °C accuracy is +/-14%

## 1.7 LED Drivers

Min and Max values: Tc= -40 °C to 85 °C,  $DV_{DD}$ =1.8 V+/-5%,  $ALV_{DD}$ =1.8 V+/-5%,  $DHV_{DD}$ =3.3 V+/-5%,  $AHV_{DD}$ =3.3 V+/-5% unless otherwise noted. Typical values: Tc=25 °C,  $DV_{DD}$ ,  $ALV_{DD}$ =1.8 V,  $AHV_{DD}$ =3.3 V

#### Table 1-7. LED Drivers

| Parameter                                                                                                            | Conditions                                                              | Minimum          | Typical | Maximum | Units |

|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------|---------|---------|-------|

| Headroom required <sup>1</sup>                                                                                       | At 2A full scale                                                        | —                | -       | 0.3     | V     |

| Maximum allowable voltage headroom <sup>2</sup>                                                                      |                                                                         | _                | _       | 5.5     | V     |

| Rise/fall time <sup>3</sup>                                                                                          | 20-80% Into 1 $\Omega$ electrical output, no snubber network            | —                | _       | 200     | ns    |

| NOTES:                                                                                                               |                                                                         |                  |         |         |       |

| 1. Required headroom scales with output current, maximum output current requires maximum headroom (see Section 2.3). |                                                                         |                  |         |         |       |

| 2. To prevent damage at outp                                                                                         | ut pins do not exceed this voltage. Also verify power sequencing and po | wer dissipation. |         |         |       |

3. Guaranteed by design

#### Table 1-8.Output Current DACs

| Parameter                                 | Conditions                                                          | Minimum          | Typical | Maximum | Units |

|-------------------------------------------|---------------------------------------------------------------------|------------------|---------|---------|-------|

| Resolution                                |                                                                     | —                | 10      | —       | bits  |

| Conversion rate                           |                                                                     | _                | 12.5    | —       | Msps  |

| Full scale IOUTX                          | Referred to the current output                                      | _                | 2       | _       | Α     |

| IOUTX absolute accuracy                   | Referred to the current output <sup>1</sup>                         | -8               | —       | 8       | %     |

| <b>NOTES:</b><br>1. For driver headroom > | • specified in Table 1-7. Measured at 1000 mA. At Tc= 120 °C accura | acy is -8% to +1 | 0%      | L       | 1     |

#### Table 1-9. Scale DACs

| Parameter           | Conditions                                                 | Minimum | Typical | Maximum | Units |

|---------------------|------------------------------------------------------------|---------|---------|---------|-------|

| Resolution          |                                                            | _       | 6       | _       | bits  |

| Minimum scale value | Referred to the current output, equivalent to code 000000b | 180     | 200     | 220     | mA    |

| Maximum scale value | Referred to the current output, equivalent to code 111111b | 1.775   | 2       | 2.2     | А     |

| Scale step          | Referred to the current output                             | 25      | 28.6    | 31      | mA    |

## 1.8 DC-DC Converters Reference Generators

Min and Max values: Tc= -40 °C to 85 °C,  $DV_{DD}$ =1.8 V+/-5%,  $ALV_{DD}$ =1.8 V+/-5%,  $DHV_{DD}$ =3.3 V+/-5%,  $AHV_{DD}$ =3.3 V+/-5% unless otherwise noted. Typical values: Tc=25 °C,  $DV_{DD}$ ,  $ALV_{DD}$ =1.8 V,  $AHV_{DD}$ =3.3 V

| Table 1-10. | DC-DC Converters Reference Generators |

|-------------|---------------------------------------|

| 14010 1 101 |                                       |

| Parameter                         | Conditions                                                                                               | Minimum | Typical | Maximum | Units |

|-----------------------------------|----------------------------------------------------------------------------------------------------------|---------|---------|---------|-------|

| Voltage compliance                | 0.5                                                                                                      | 1.2     | 1.3 V   | V       |       |

| DAC resolution                    |                                                                                                          | _       | 9       | —       | bits  |

| DAC DNL                           |                                                                                                          | -1.3    | _       | 1.3     | LSB   |

| DAC full scale                    | (regref_setup[1]=0b)                                                                                     | _       | 100     | 110     | μA    |

| DAC full scale                    | (regref_setup[1]=1b)                                                                                     | _       | 200     | 220     | μA    |

| DC-DC Converter Headroom<br>Error | Configured as per Table 2-4 using a Texas Instruments TPS63020 DC-DC converter and decimation set to 64. | -20     | _       | +20     | mV    |

## 1.9 Internal Temperature Sensor

Typical values: Tc=-40 °C to 100 °C, DV<sub>DD</sub>, ALV<sub>DD</sub>=1.8 V, AHV<sub>DD</sub>=3.3 V

Table 1-11. Internal Temperature Sensor

| Parameter                                                                | Conditions | Minimum | Typical    | Maximum | Units |

|--------------------------------------------------------------------------|------------|---------|------------|---------|-------|

| Range                                                                    |            | _       | -40 to 125 | _       | °C    |

| Temperature step                                                         |            | _       | 0.65       | _       | °C    |

| Absolute accuracy <sup>1</sup>                                           |            | -10     | _          | +10     | °C    |

| NOTES:                                                                   |            |         |            |         |       |

| 1. After system calibration at room temperature (one point calibration). |            |         |            |         |       |

## 1.10 Light Sources Alarm

**Min and Max values:** Tc= -40 °C to 85 °C,  $DV_{DD}$ =1.8 V+/-5%,  $ALV_{DD}$ =1.8 V+/-5%,  $DHV_{DD}$ =3.3 V+/-5%,  $AHV_{DD}$ =3.3 V+/-5% unless otherwise noted. **Typical values:** Tc=25 °C,  $DV_{DD}$ ,  $ALV_{DD}$ =1.8 V,  $AHV_{DD}$ =3.3 V

#### Table 1-12. Light Sources Alarm

| Parameter                                                                                                         | Conditions | Minimum | Typical | Maximum | Units |

|-------------------------------------------------------------------------------------------------------------------|------------|---------|---------|---------|-------|

| Light sensor alarm thresholds <sup>1</sup>                                                                        |            | 50      | _       | 200     | mV    |

| Threshold accuracy                                                                                                |            | _       | +/-15   | —       | mV    |

| Alarm response time                                                                                               |            | _       | 5       | _       | μs    |

| <b>NOTES:</b><br>1. Threshold can be programmed through register alarm_setup0/1 to 50 mV, 100 mV, 150 mV, 200 mV. |            |         |         |         |       |

## 1.11 CMOS Pins Characteristics

Min and Max values: Tc= -40 °C to 85 °C,  $DV_{DD}$ =1.8 V+/-5%,  $ALV_{DD}$ =1.8 V+/-5%,  $DHV_{DD}$ =3.3 V+/-5%,  $AHV_{DD}$ =3.3 V+/-5% unless otherwise noted. Typical values: Tc=25 °C,  $DV_{DD}$ ,  $ALV_{DD}$ =1.8 V,  $AHV_{DD}$ = +3.3 V

| Parameter                                                                                                                                            | Conditions                     | Minimum               | Typical | Maximum               | Units |

|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-----------------------|---------|-----------------------|-------|

| V <sub>IH</sub> <sup>1</sup>                                                                                                                         |                                | 0.65 DV <sub>DD</sub> | —       | 3.63                  | V     |

| V <sub>IL</sub>                                                                                                                                      |                                | 0                     | —       | 0.35 DV <sub>DD</sub> | V     |

| V <sub>OH</sub>                                                                                                                                      |                                | DV <sub>DD</sub> -0.4 | —       | DV <sub>DD</sub>      | V     |

| V <sub>0L</sub>                                                                                                                                      |                                | 0                     | —       | 0.4                   | V     |

| Rise/fall time <sup>2</sup>                                                                                                                          | Maximum load of 5 pF. SPI mode | —                     | 3       | —                     | ns    |

| NOTES:         1. Digital pins are 3.3 V (+/-10%) tolerant         2. In I <sup>2</sup> C mode, rise/fall time depends on load and pull up resistor. |                                |                       |         |                       |       |

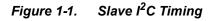

# 1.12 Slave I<sup>2</sup>C Timing Specifications<sup>1,2</sup>

Min and Max values: Tc= -40 °C to 85 °C,  $DV_{DD}$ =1.8 V+/-5%,  $ALV_{DD}$ =1.8 V+/-5%,  $DHV_{DD}$ =3.3 V+/-5%,  $AHV_{DD}$ =3.3 V+/-5% unless otherwise noted. Typical values: Tc=25 °C,  $DV_{DD}$ ,  $ALV_{DD}$ =1.8 V,  $AHV_{DD}$ =3.3 V

| Parameter                                                                            | Symbol (refer to figure below) | Minimum | Typical | Maximum | Units |

|--------------------------------------------------------------------------------------|--------------------------------|---------|---------|---------|-------|

| Clock Frequency, SCL_M                                                               | fscl_master                    | -       | _       | 3.4     | MHz   |

| Clock Pulse Width Low                                                                | t <sub>LOW</sub>               | 160     | _       | —       | ns    |

| Clock Pulse Width High                                                               | <sup>t</sup> ніgн              | 60      | _       | —       | ns    |

| Clock Low to Data Out Valid                                                          | t <sub>AA</sub>                | 0       | _       | 70      | ns    |

| Start Hold Time                                                                      | <sup>t</sup> hdsta             | 160     | _       | —       | ns    |

| Start Set-up Time                                                                    | <sup>t</sup> susta             | 160     | _       | —       | ns    |

| Data In Hold Time                                                                    | <sup>t</sup> hddat             | 0       | _       | —       | ns    |

| Data In Set-up Time                                                                  | tsudat                         | 10      | _       | —       | ns    |

| Outputs (SDA_M, SCL_M, SDA_S and SCL_S) internal pull-up resistor value <sup>3</sup> | R <sub>PULL-UP</sub>           | _       | 250     | -       | kΩ    |

| Stop Set-up Time                                                                     | tsusto                         | 160     | _       | _       | ns    |

| Data Out Hold Time                                                                   | t <sub>DH</sub>                | 5       | _       | —       | ns    |

| NOTES:                                                                               |                                |         |         |         |       |

| 1. Guaranteed by design and characterization.                                        |                                |         |         |         |       |

| 2. Specified at recommended operating conditions.                                    |                                |         |         |         |       |

| 3. 4.7 k $\Omega$ should be added externally.                                        |                                |         |         |         |       |

#### Table 1-14. Slave I<sup>2</sup>C Timing Specifications<sup>1,2</sup>

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

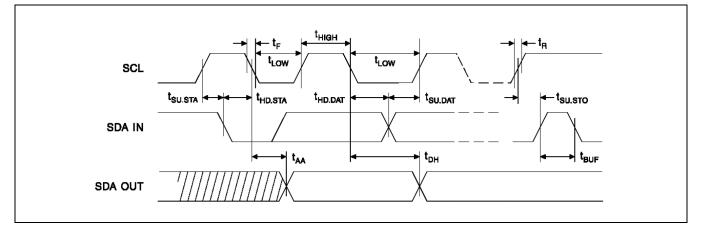

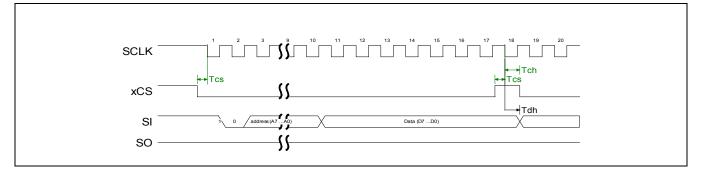

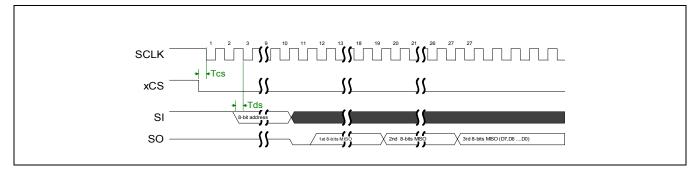

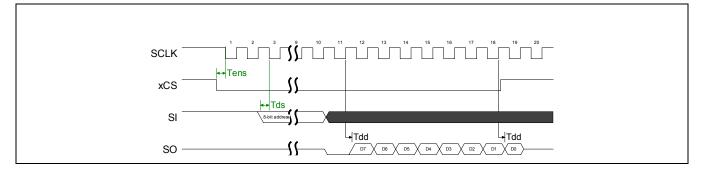

## 1.13 High Speed Serial Interface Timing Specifications

Min and Max values: Tc= -40 °C to 85 °C,  $DV_{DD}$ =1.8 V+/-5%,  $ALV_{DD}$ =1.8 V+/-5%,  $DHV_{DD}$ =3.3 V+/-5%,  $AHV_{DD}$ =3.3 V+/-5% unless otherwise noted. Typical values: Ta=25 °C,  $DV_{DD}$ ,  $ALV_{DD}$ =1.8 V,  $AHV_{DD}$ =3.3 V

| Parameter                                            | Symbol (refer to figure below) | Minimum | Typical | Maximum | Units |

|------------------------------------------------------|--------------------------------|---------|---------|---------|-------|

| Clock Frequency                                      | fclk=1/Tclk                    | _       | —       | 3.4     | MHz   |

| Data in to clk hold time                             | Tdh                            | 160     | —       | —       | ns    |

| Data in to clk set-up time                           | Tds                            | 60      | —       | —       | ns    |

| Enable to clk set up time                            | Tcs                            | 0       | —       | 70      | ns    |

| Enable to clk hold time                              | Tch                            | 160     | —       | —       | ns    |

| Read data output valid following rising edge of SCLK | Tdd                            | 160     | —       | —       | ns    |

| SCLK duty cycle                                      |                                | 45      | —       | 55      | %     |

| <b>NOTES:</b><br>1. Maximum output capac             | itance of 30 pF.               | 1       |         |         | 1     |

Table 1-15. High speed serial interface timing specifications

#### Figure 1-2. Serial Interface Sequential Write

### High Performance RGB Driver for DLP/LCD/LCoS Projectors

#### Figure 1-3. Serial Interface Random Write

Figure 1-4. Serial Interface Sequential Read

Figure 1-5. Serial Interface Random Read

#### Rev V4

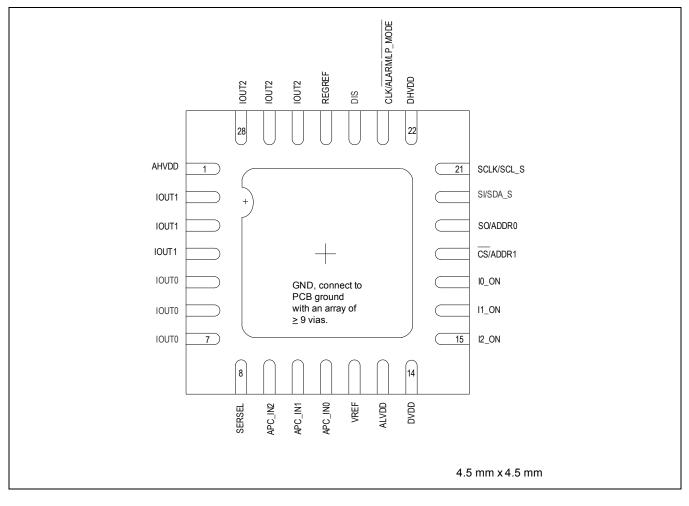

## 1.14 M08888 Pinout

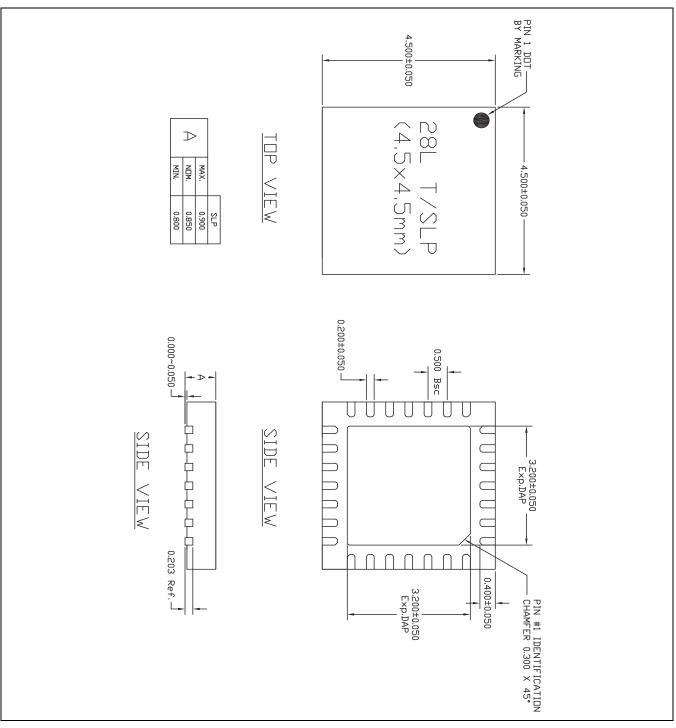

The M08888 is packaged in a 4.5 x 4.5 mm 28-pin QFN package with 0.5 mm pin pitch.

#### Figure 1-6. M08888 Pinout

13

### High Performance RGB Driver for DLP/LCD/LCoS Projectors

Rev V4

| Pins       | Name                 | Туре                    | Function                                           |

|------------|----------------------|-------------------------|----------------------------------------------------|

| 1          | AHVDD                | Supply                  | 3.3 V analog supply                                |

| 2, 3, 4    | IOUT1                | Analog                  | Channel 1 output                                   |

| 5, 6, 7    | IOUT0                | Analog                  | Channel 0 output                                   |

| 8          | SerSEL               | CMOS (w/ pulldown)      | Serial interface select (L=I <sup>2</sup> C,H=SPI) |

| 9, 10, 11  | APC_IN               | Analog                  | Monitor PD inputs (assignable)                     |

| 12         | VREF                 | Analog                  | Current reference generator                        |

| 13         | ALVDD                | Supply                  | 1.8 V analog supply                                |

| 14         | DVDD                 | Supply                  | 1.8 V digital supply                               |

| 15         | 12_ON                | CMOS (w/ pulldown)      | Turns on driver 2                                  |

| 16         | 11_ON                | CMOS (w/ pulldown)      | Turns on driver 1                                  |

| 17         | 10_ON                | CMOS (w/ pulldown)      | Turns on driver 0                                  |

| 18         | CS/ADDR0             | Open Drain (w/ pull-up) | Serial enable/l <sup>2</sup> C address0            |

| 19         | SO/ADDR1             | Open Drain (w/ pull-up) | Serial data out/I <sup>2</sup> C address1          |

| 20         | SI/SDA_S             | Open Drain (w/ pull-up) | Serial data in/l <sup>2</sup> C data slave         |

| 21         | SCLK/SCL_S           | Open Drain (w/ pull-up) | Serial clock/I <sup>2</sup> C clock slave          |

| 22         | DHVDD                | Supply                  | 3.3 V digital supply                               |

| 23         | CLK_IN/ALARM/LP_MODE | CMOS (w/ pulldown)      | CLK_IN pin or ALARM or P_MODE pin                  |

| 24         | DIS                  | CMOS                    | Disable Pin                                        |

| 25         | REGREF               | Analog                  | DC-DC converter control voltage                    |

| 26, 27, 28 | IOUT2                | Analog                  | Channel 2 output                                   |

|            | GND                  | Supply                  | Ground                                             |

#### Table 1-16. Pin List and Descriptions

PD means pulled down, PU means pulled up.

4.7 µF + 100nF should be used on each of the M08888 supply.

High Performance RGB Driver for DLP/LCD/LCoS Projectors

Rev V4

# 1.15 Package Information

#### Figure 1-7. Package Information

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

# 2.0 Functional Description

The M08888 is a highly integrated LED/laser driver for LCD/LCoS/DLP projection display applications. It provides control and monitoring of up to three LEDs/lasers, a temperature sensor and control of external DC-DC converters for optimal laser/led supply voltage.

Each Laser/LED output consists of a 10 bit DAC which controls a high efficiency driver. If the desired maximum current is less than 2A the output resolution can by improved by a 6 bit independent scaling DAC.

The output stages require only 300 mV of headroom between the M08888 output and the Laser/LED cathode when driving 2 amperes. The headroom requirement can be scaled proportionally lower for lower currents.

The M08888 also incorporates safety and alarm features and a temperature monitor with 8 bit resolution.

The M08888 internal registers are loaded from an external micro controller through a slave I<sup>2</sup>C interface or a 4-wire high speed interface. The host micro controller can monitor the temperature sensor and read back the analog to digital converter outputs and status registers using either serial interface.

## 2.1 Operating Modes

The M08888 can operate in 3 different optical power control modes. The power control modes are open loop (OL) and 2 automatic power control (APC) modes: continuous power control (CPC) and integrating power control (IPC).

Different output channels can have different operating modes. Some channels may be configured as Open Loop and some channels may be configured to use APC (either CPC or IPC).

Open Loop mode is the simplest mode of operation and the Laser/LED current is set by writing the desired current to the output DAC.

The 2 automatic power control modes (APC) use monitor photodiode feedback to accurately adjust the Laser/LED output power to make the current from a photodiode match a target current. With APC control temperature compensation of the Laser/LED is automatic and color balance is simplified.

The user can select the polarity of the monitor photodetector if an APC mode is selected. By default the M08888 accepts a current source monitor photodetector (MPD) tied to the positive supply. It is possible to accept current sink MPD by selecting ipc\_setup[4]=1b.

Configuration of the M08888 timer settings and pin 23 configuration will also affect optical power control.

### 2.1.1 Open Loop Output Control

In open loop mode the current for each Laser/LED is stored in register (ioutx[9:0]). The M08888 will shift the contents of ioutx[9:0] and ioutx\_scale[5:0] registers to the output DAC when pin  $lx_ON$  goes high and the output will then sink the programmed current through the Laser/LED.

<sup>16</sup>

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

### High Performance RGB Driver for DLP/LCD/LCoS Projectors

By changing the scale setting ioutx\_scale the full 10 bits of settability can be retained even for low Laser/LED currents. The scale can be changed on a frame by frame basis but when ioutx\_scale is changed the rise time of the output stage will be significantly slower during the first  $Ix_ON$  period in which the change in the scale is made. The rise time will return to its normal value in subsequent  $Ix_ON$  periods if the scale is not changed.

The M08888 includes timers that can be used to delay, pulse width modulate or clock the Open Loop output signal. See Section 2.4 for a description of how to use these features.

When pin 23 operates in  $\overline{LP\_MODE}$  (input\_ctrl[6:5]=10b) the scale value of each channel can be different for the different pin 23 states. These scales are set in iout**x**\_scale[5:0] (pin 23=H) and iout**x**\_scale\_LP[5:0] (pin 23=L).

Table 2-1.

Basic Register Configuration for Open Loop Control (when REGREF is not controlling a DC-DC Converter)

| Name                          | Address                             | Recommend<br>Setting | Description                                                                                         |

|-------------------------------|-------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------|

| out_ctrl <b>x</b>             | 0x05[7],0x06[7],<br>0x07[7]         | 1b                   | Set outputs to Open Loop Control if Regref is not used to control a DC-DC converter at this output. |

| pd_fe                         | 0x0A[0]                             | 1b                   | Power down photodiode amplifier (if all channels are under open loop control)                       |

| iout <b>x</b> _msb            | 0x10[1:0], 0x14[1:0],<br>0x18[1:0]  | xxb                  | Two most significant bits of output current setting                                                 |

| iout <b>x</b> _lsb            | 0x11, 0x15,0x19                     | xxh                  | Eight least significant bits of output current setting                                              |

| iout <b>x</b> _scale          | 0x12, 0x16, 0x1A                    | 11xxxxxb             | Set the scaling of the output currents                                                              |

| iout <b>x</b> _scale_lp       | 0x13, 0x17, 0x1B                    | 11xxxxxb             | Set the scaling of the output currents in Low Power mode                                            |

| apc0_ch<br>apc1_ch<br>apc2_ch | 0x34[1:0]<br>0x34[3:2]<br>0x34[5:4] | 11b                  | Disable APC input for selected channel                                                              |

### 2.1.2 Automatic Power Control

Automatic power control (APC) can keep the laser/led power constant and the color balanced by comparing the monitor photodetector (RGB color sensor) currents to target values programmed into the 13-bit target DACs.

At power-up the APC can be enabled/disabled independently for each channel by setting apc\_ctrl0[5:0]=11. For channels with disabled APC the laser/led currents are controlled through the serial interface using bits iout**x**[9:0].

It is possible to freeze the APC loop for each channel by using  $apcx_freeze[0]$ . In this case the M08888 will stop updating the *IOUTx* currents independently of the state of *Ix\_ON* pins. The photodiode (RGB sensor) target values are programmed via the serial interface in registers target2[12:0], target1[12:0] and target0[12:0] respectively for *IOUT2, IOUT1* and *IOUT0*. When the corresponding color is turned on as signaled by the transition of *I0\_ON*, *I1\_ON* or *I2\_ON* from low to high the LED/Laser drive currents are automatically adjusted up or down to always make the photodetector current (RGB sensor current) match the target current.

If desired, these target currents can be adjusted on a frame by frame basis to optimize contrast and save battery power depending on the brightness required for a particular frame.

<sup>17</sup>

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

#### High Performance RGB Driver for DLP/LCD/LCoS Projectors

Rev V4

The target values are stored in registers target2[12:0], target1[12:0] and target0[12:0] respectively for *IOUT2*, IOUT1 and IOUT0 before the corresponding color is turned on by the transition of *I2\_ON*, *I1\_ON* or *I0\_ON* from low to high. This allows for the control of the LED/laser power in real time on a frame by frame basis.

When one of the *Ix\_ON* signals is enabled (low to high transition), the target DAC value for that input is activated and the incoming monitor photodetector current is selected by the analog multiplexer from *APC\_IN0*, *APC\_IN1* or *APC\_IN2*. The monitor photodetector input is assigned to an output using apc\_ctrl[5:0].

Each Laser/LED can have its own photodetector or all the Lasers/LEDs can share a single broadband photodetector. For example, if a single broadband photodetector is used and connected to APC\_IN0 all the apc\_ctrl0[5:0] should be set to 00b. It should be noted that the index in the APC registers does not refer to the input channel but to the Laser/LED output channel. If the monitor photodetector feedback for IOUT2 is tied to APC\_IN0 then apc\_ctrl[5:4]=00 and the settings for the monitor photodetector should be programmed in the APC registers with index 2.

If more then one laser is turned on (2 or 3 of I0\_ON, I1\_ON or I2\_ON are high at the same time) the M08888 freezes the update of the APC loop for as long as more then one of the  $Ix_ON$  signals are high. This prevents the APC loop from using incorrect photodetector information in case a single photodetector is used. In the case of multiple  $Ix_ON$  simultaneously the optical power tracked and adjusted is that of the channel corresponding to the last/ $x_ON$  transitioning high. It should be noted that 2 or more low to high transitions of any of the  $I0_ON$ ,  $I1_ON$  or  $I2_ON$  within 500 ns of each other would violate internal timing and will result in unpredictable operation. Care should be taken to prevent damage to the part when multiple lasers are enabled. The power dissipation of the M08888 should be kept below the level that, when multiplied by the thermal resistance of the package in the system and added to the maximum ambient temperature, does not exceed 125 °C.

The maximum photodiode current supported by the M08888 is 3.25 mA. The full scale value of the target DAC is 3.25 mA with a resolution of 13 bits (390 nA step size). As an example, if the maximum current from the photodiode is 200  $\mu$ A then the possible target values are up to 512 decimal (200  $\mu$ A/390 nA). In this example the maximum target value for targetx[12:0] would be 200h.

Readback of the output current DAC of each channel is possible by strobing the DACs using strbalarm\_ctrl[1] and reading registers rb\_ioutx[9:0]

When pin 23 is set to  $\overline{LP\_MODE}$  (input\_ctrl[6:5]=10b) the target power value will be controlled by the state of pin 23. When pin 23 is high the Laser/LED current will be adjusted until the monitor photodiode current matches the target in register targetx[12:0] and when pin 23 is low the Laser/LED current will be adjusted until the monitor photodiode current matches the target in register targetx \_LP[12:0].

The M08888 is capable of accepting also current sink type monitor photodetector typical of LCOS panels. This can be done by setting register ipc\_setup[4]=1b. When sink MPD is selected the mirror ratio can be selected between 1:1 and 4:1 by setting bit ipc\_setup[5].

The MPD can have a maximum capacitance of up to 300 pF however in this case the M08888 will operate only with a single broadband photodetector.

#### 2.1.2.1 Continuous Power Control

In continuous power control (CPC) mode, the M08888 continuously compares the monitor photodetector current to a target value and makes monitor photodiode current match the target value by adjusting the current in the laser/ LED. For example, if the monitor photodetector current is below the target then the Laser/LED current is increased. The sign of this operation can be inverted using input\_ctrl[4] (but it should not be changed unless it is certain that there is an inversion in the monitor photodiode signal).

<sup>18</sup>

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

#### High Performance RGB Driver for DLP/LCD/LCoS Projectors

Rev V4

The CPC loop is designed to settle to the desired output power in less than 50  $\mu$ s. To achieve optimal settling time, the CPC loop must be adjusted to the laser/monitor photodetector characteristics. This is done using the settings in apcx\_ctrl0, apcx\_ctrl1 and apcx\_ctrl2.

To further reduce the settling time the user can program the initial current from which the CPC loop will start. This can be 0, the value programmed in ioutx[9:0] register or the value to which the CPC had converged during the previous frame. The selection of the initial current is done using register iturnonx[1:0] (apcx\_ctrl1[3:2]). Starting from the previously determined value will substantially accelerate settling time since it is likely that it will be starting at the proper level.

It is possible to "freeze" the APC loop for each channel by using  $apcx\_ctrl0[0]$ . When  $apcx\_ctrl0[0]=1b$  the M08888 will stop updating the *IOUTx* currents irregardless of the state of *Ix\_ON* pins. It is possible also to delay operation the CPC loop immediately following the light source turn-on. This will allow the DC-DC converter to settle to the proper voltage before the APC starts adjusting the current. The CPC delay time can be programmed using register  $apcx\_ctrl0[2:1]$ .

| Name                 | Address                     | Recommend<br>Setting | Description                                                                                                                                                                                 |

|----------------------|-----------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| out_ctrl <b>x</b>    | 0x05[7],0x06[7],<br>0x07[7] | 1b                   | Set output to Closed Loop Control                                                                                                                                                           |

| loop select          | 0x34[6]                     | 1b                   | Select CPC loop control                                                                                                                                                                     |

| apc0_ch              | 0x34[1:0]                   |                      | Select which photodiode (RGB sensor) input will control which output. Setting depends on                                                                                                    |

| apc1_ch              | 0x34[3:2]                   | xxb                  | hardware connection to photodiode(s) and which channels will use APC control. See Register description for details.                                                                         |

| apc2_ch              | 0x34[5:4]                   |                      |                                                                                                                                                                                             |

| target <b>x</b> _msb | 0x35, 0x37, 0x39            | 000x xxxxb           | Set the target at desired level. The LED drive current will be adjusted up or down until the photodiode current is equal to the target current for the channels that are controlled by CPC. |

| target <b>x</b> _lsb | 0x36, 0x38, 0x3A            | xxh                  |                                                                                                                                                                                             |

| apc0_ctrl2           | 0x47                        | xxh                  | Set the length in clock counts of the initial, mid and min step intervals. Set the delay for the                                                                                            |

| apc1_ctrl2           | 0x44                        |                      | clock divider. The decimation factor and clock divider will also affect interval lengths.                                                                                                   |

| apc2_ctrl2           | 0x41                        |                      |                                                                                                                                                                                             |

| apc0_ctrl1           | 0x48                        | xxh                  | Set the step size of the change in LED drive current for the initial and mid intervals. Set the                                                                                             |

| apc1_ctrl1           | 0x45                        |                      | initial LED current to be 0 mA, the ending value of the previous I_on period or the value set                                                                                               |

| apc2_ctrl1           | 0x42                        |                      | in iout <b>x</b> register. Set the clock divider.                                                                                                                                           |

| apc0_ctrl0           | 0x49                        | xxx00xx0b            | Set the decimation factor (mid and min count changes will occur at rate divided by the                                                                                                      |

| apc1_ctrl0           | 0x46                        |                      | decimation factor). Set the WAIT states (APC will not change LED current during WAIT                                                                                                        |

| apc2_ctrl0           | 0x43                        |                      | states).                                                                                                                                                                                    |

| Table 2-2. | Basic Register Configuration for CPC Control |

|------------|----------------------------------------------|

|------------|----------------------------------------------|

#### 2.1.2.2 Integral Power Control

Integral power control (IPC) can be enabled by setting registers apc\_ctrl[6]=0b.

The working principle of integral power control is to mimic the behavior of the human eye which integrates the optical power over the frame period. This is achieved in the M08888 by charging a capacitor with the monitor photodetector current.

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

#### High Performance RGB Driver for DLP/LCD/LCoS Projectors

Rev V4

When *Ix\_ON* goes high the M08888 will drive the Laser/LED with a current defined by register ioutx[9:0]. The monitor photodiode current will charge an internal capacitor until its voltage matches an internal reference voltage (~0.8 V) at which time a counter is incremented and the capacitor is discharged. The monitor photodiode current continues to charge the capacitor and increment the counter until the count matches the target set by the user in registers targetx[9:0]. Once the counter reaches the value set by the user the M08888 stops driving the Laser/LED. By adjusting the count higher or lower the brightness of a frame can be adjusted. The target counter has 10bits and the M08888 can distinguish between 1024 different power levels. The target registers are the same of the CPC target registers but the resolution in IPC mode is limited to 10 bits instead of 13 bits.

In order to maximize the dynamic range and be able to utilize the entire 10bits the user must select the proper mirroring ratios for the monitor photodetector current ( $ipdx_sel[4:0]$ ), the charging current ( $ichx_sel[4:0]$ ) and the value of the capacitance ( $capx_sel[3:0]$ ). The settings of these bits will depend on the frame (or subframe) duration and on the monitor photodetector current.

If it is desired to typically have the LED on for 1/2 the frame time then the registers should be configured such that:

1/2 x FR/512 = 0.8 V x Cch / Ich

where FR is the frame or subframe rate, Cch is the charging capacitors selected through cap $x_sel[3:0]$ , and Ich is the resulting charging current obtained by multiplying the monitor photodetector current by the ipd $x_sel[4:0]$  and by the ich $x_sel[4:0]$  mirroring ratios. The factor of 512 is length of the 10 bit range.

Cch = 25 pF + N x 2.5 pF where N is the setting of capx\_sel[3:0].

Ich =  $(I_{MPD} / ipdx_{sel}[4:0]) \times ichx_{sel}[4:0]$  where  $I_{MPD}$  is the monitor photodiode current

**Example:** Assume that the monitor photodiode current is  $150 \,\mu$ A when the LED is on at the desired amplitude, the *lx\_ON* time is 1 ms and it is desired that the LED be on approximately 50% of this time. The mirroring ratio should be set to the 200  $\mu$ A range ichx\_sel[4:0] = 00001b, choose a Cch = 25 pF with ichx\_sel[4:0] = 00000b (any other value is also OK but using the default value means this register never needs to be written), choose a mirroring ratio such that the Cch can be charged to 0.8 V several hundred times in 0.5 ms. (if it is desired that it be charged ~250 times in 0.5 ms then:

0.5 ms/250 =0.8 V x 25 pF /((150 μA / 200 μA) x ich**x**\_sel[4:0]) 0.002 ms = 26.67e-12 / ich**x**\_sel[4:0] ich**x**\_sel[4:0] = 2.667e-5 / 2 which is between 10 μA and 20 μA so set ich**x**\_sel[4:0] =00001b

As in CPC mode, when pin23 operates in  $\overline{LP\_MODE}$  (input\_ctrl[6:5]=10b) the target power value can be changed by toggling pin23. When pin 23 is high the Laser/LED current will be on until the monitor photodiode count matches the target in register targetx[9:0] and when pin 23 is low the Laser/LED current will be on until the monitor photodiode count matches the targetx \_LP[9:0].

The monitor photodiode input can be changed from sinking to sourcing at ipc\_setup[4] and an additional scaling factor of 4:1 is available at ipc\_setup[5].

<sup>20</sup>

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

| Name                                         | Address                              | Recommend<br>Setting | Description                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|----------------------------------------------|--------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| ipc_setup[4]                                 | 0x4Ah[4]                             | 0b or 1b             | M08888 sinks MPD current (1b) or sources MPD current (0b)                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| out_ctrl <b>x</b>                            | 0x05[7],0x06[7],<br>0x07[7]          | 1b                   | Set output to Closed Loop Control                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| loop select                                  | 0x34[6]                              | 0b                   | Select IPC loop control                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| apc0_ch<br>apc1_ch<br>apc2_ch                | 0x34[1:0]<br>0x34[3:2]<br>0x34[5:4]  | xxb                  | Select which photodiode (RGB sensor) input will control which output. Setting depends on hardware connection to photodiode(s) and which channels will use APC control. See Register description for details.                                                                                                                                                                                                               |  |  |  |  |  |

| target <b>x</b> _msb<br>target <b>x</b> _lsb | 0x35, 0x37, 0x39<br>0x36, 0x38, 0x3A | 000xxxxxb<br>xxh     | Set the target to the desired count. The LED drive current set in the ioutx register will be or<br>until the current from the ichx current mirror charges the capacitor set at ipcx_ctrl2[3:0] to<br>0.8 V the number of times set in this target register (the capacitor at pcx_ctrl2[3:0] is<br>discharged every time the 0.8 V comparator is tripped and recharging begins again until the<br>target count is reached). |  |  |  |  |  |

| iout <b>x</b> _msb                           | 0x10[1:0],<br>0x14[1:0], 0x18[1:0]   | xxb                  | Two most significant bits of output current setting                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| iout <b>x</b> _lsb                           | 0x11, 0x15,0x19                      | xxh                  | Eight least significant bits of output current setting                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| iout <b>x</b> _scale                         | 0x12, 0x16, 0x1A                     | 11xxxxxb             | Set the scaling of the output currents                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| ipd <b>x</b> _sel                            | 0x4C[4:0]<br>0x4F[4:0]<br>0x52[4:0]  | x xxxxb              | Select a setting that is greater than the peak current expected from the monitor photodiode.<br>Choosing a lower amplitude setting will give more resolution/accuracy in setting the IPC target.                                                                                                                                                                                                                           |  |  |  |  |  |

| ich <b>x</b> _sel                            | 0x4D[4:0]<br>0x50[4:0]<br>0x53[4:0]  | x xxxxb              | Select a current range that can charge the IPC capacitor several hundred (but <511) times during the <i>Ix_ON</i> time.                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

#### Table 2-3. Basic Register Configuration for IPC Control

## 2.2 Outputs

### 2.2.1 LASER/LED Current DACs

The M08888 includes three monotonic DACs which generate the currents for the three LED output drivers.

The three DACs have a maximum range from 0 to 2A, a resolution of 10 bits and a maximum update rate of 12.5 MSPS. The output rise time will be limited by the M08888 output current driver unless a single DC-DC converter is used for more than one Laser/LED, in which case the DC-DC converter settling time and overall supply loop behavior may determine the output rise time.

The full scale of each output DAC can be programmed through the ioutx\_scale[5:0] bits independently for each channel. The scale DAC changes the full scale of each output current DAC from a minimum of 200 mA to a maximum of 2A in steps of 28.57 mA. At power-up the scale DACs are set at maximum scale (2A).

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

Rev V4

### 2.2.2 Output Current Drivers

The integrated output current drivers deliver the DAC currents to the Lasers/LEDs.

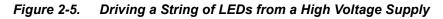

Each Laser/LED driver output (*IOUTx*) is controlled by the corresponding ON signal ( $Ix_ON$ ) and the PWM and MPG setting as described later. Rise/fall time of the driver is typically 200 ns into a resistive electrical load connected to a stable supply voltage. If a DC-DC converter is employed the response time of the current output may also depend on the response time of the DC-DC converter and the series resistance of the light sources. The rise and fall time is specified for any transition of the ioutx[9:0] registers for a constant ioutx\_scale[5:0] code.

The drivers require a worst case headroom of 300 mV. The headroom is proportionally lower at lower drive currents.

The M08888 typical driver headroom follows the following equation:

VLDD = 150 m $\Omega$  x IOUT

The voltage at the laser driver output should never exceed 5.5 V. An external resistor should be used between the laser/LED cathode and ground to provide a small leakage current into the light source allowing the voltage at the *IOUTx* to be reduced from the anode voltage by the laser/LED voltage drop. The value of the resistor should be chosen such that the current flowing is enough to create a voltage drop on the laser while keeping the laser current far below threshold or, in the case of LEDs, low enough so as to not cause light pollution in the system.

### 2.2.3 Recommended Snubbing Network at *IOUTx* Pins

A snubbing network of 1  $\mu$ F in series with 1.5  $\Omega$  should be placed in parallel with the LED/Laser at each *IOUTx* pin. The inductance in series with the LED/Laser should be less than 500 nH.

## 2.3 Controlling the Output Voltage to Optimize Power Consumption

The system power dissipation will be dominated by the Laser/LED current and the bias voltage of the Laser/LED. For each ampere of Laser/LED current, each 100 mV of excess Laser/LED bias voltage results in 100 mW of wasted power.

The M08888 minimizes the voltage drop on the output stage and optimizes overall power dissipation by adjusting the anode voltage of the light sources through the external DC-DC converter. Given the expected maximum current for a particular LED/laser on a channel, the user can program the headroom required for each channel based on the equations above (Section 2.2.2) to optimize system power. Whether or not the M08888 controls the DC-DC converter output voltage the required headroom of the M08888 outputs must be maintained when the corresponding  $Ix_ON$  is high (see Section 2.2.2).

### 2.3.1 Control of External DC-DC Converters with the M08888

An external DC-DC converter is controlled by the M08888 by connecting pin *REGREF* to the DC-DC converter feedback pin.

Typical register settings to allow control of an external DC-DC converter are shown below.

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

| Name          | Address             | Recommended Setting | Description                                                                                                                                                                             |

|---------------|---------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| selfcal_hr    | 0x00[4]             | 1b                  | Power-up REGREF circuitry                                                                                                                                                               |

| opmode_ctrl1  | 0x01[7]             | 1b                  | Set DC-DC output to minimum when all Ix_ON are low                                                                                                                                      |

| out_ctrlx     | 0x05, 0x06,<br>0x07 | 8Ch                 | Recommended Configuration                                                                                                                                                               |

| regref_setup  | 0x24                | 00h                 | Set REGREF operating mode                                                                                                                                                               |

| regref2_ctrl1 | 0x27                | FFh                 | Set the headroom at <i>IOUT2</i> to 310 mV and the decimation factor to 2048. Lower headroom values can be used depending on the maximum <i>IOUT2</i> output current. See section 2.2.2 |

| regref2_ctrl0 | 0x28                | 44h                 | Set the DAC update rate and the starting value at IOUT2.                                                                                                                                |

| regref1_ctrl1 | 0x2B                | FFh                 | Set the headroom at <i>IOUT1</i> to 310 mV and the decimation factor to 2048. Lower headroom values can be used depending on the maximum <i>IOUT1</i> output current. See section 2.2.2 |

| regref1_ctrl0 | 0x2C                | 44h                 | Set the DAC update rate and the starting value at IOUT1.                                                                                                                                |

| regref0_ctrl1 | 0x2F                | FFh                 | Set the headroom at <i>IOUT0</i> to 310 mV and the decimation factor to 2048. Lower headroom values can be used depending on the maximum <i>IOUT0</i> output current. See section 2.2.2 |

| regref0_ctrl0 | 0x30                | 44h                 | Set the DAC update rate and the starting value at IOUT0.                                                                                                                                |

The M08888 DC-DC converter control circuitry uses a 9 bit DAC to set a feedback factor for the external DC-DC converter and adjust the anode voltage of the Laser/LEDs. The DAC is controlled by a digital filter with programmable update rate and decimation factor. The digital filter is fed by a comparator which increments or decrements the counter code depending on whether the headroom of the driver is higher or lower than the programmed headroom. The sign of this operation can be inverted through input\_ctrl[3] (this bit should not be set unless it is known that the DC-DC converter feedback path is inverted from the usual polarity). The above operations are performed automatically by the M08888 and no interaction with the M08888 is required beyond initializing the register settings as described at the beginning of this section.

Once the LED is turned off the value of the DAC inputs are stored by the M08888. The next time this LED is active, the loop will automatically start from the stored DAC value. The initial value of the DAC code can be selected through regrefx\_ctrl0[3:2] to be either the previously determined value, 0 or the value written in register regrefx\_dac. The DAC codes for each channel can be read back by using the strobe bit (strbalarm\_ctrl[1]) and registers rb\_regrefdacx[8:0].

The headroom, decimation filter and update rate can be programmed independently for each channel using regrefx\_ctrl1[7:3], regrefx\_ctrl1[2:0] and regrefx\_ctrl0[7:5] respectively.

If more then one output is being turned on at the same time, the regref will control the DC-DC converter for the headroom of the last output turned on.

If CPC is used, the user should program the headroom for the highest expected output current.

If CPC control is used there may be interactions between the settling of the DC-DC converter and the digital control method. If the settling of the DC-DC converter is such that the initial headroom is less than what is required by the Laser/LED then this may cause the CPC loop to rail (adjust the Laser/LED current to 2A) and potentially damage

M/A-COM Technology Solutions Inc. (MACOM) and its affiliates reserve the right to make changes to the product(s) or information contained herein without notice. Visit www.macom.com for additional data sheets and product information.

#### High Performance RGB Driver for DLP/LCD/LCoS Projectors

Rev V4

the Laser/LED when the voltage rises to a high enough voltage to allow unrestricted forward current conduction. The interaction of the DC-DC converter digital control method with the CPC should therefore be carefully evaluated to avoid damage to the LEDs. One way to minimize interaction between the voltage supply and the CPC control is to let the voltage supply settle before enabling CPC control of the Laser/LED current. The update of the output current in CPC mode can also be delayed using register apcx\_ctrl0[2:1] to allow proper settling of the DC-DC converter before the operation of control loop starts.

The initial update of the IDAC which controls the LED/Laser supply headroom can be delayed through registers regrefx\_ctrl0[1:0] to allow the DC-DC converter to settle.

In the case of integrating power control mode the speed of the DC-DC converter settling is not important: the light source current will be equal to the programmed current if the headroom is higher or equal to the required and will be smaller if the headroom is less then the required headroom however this will not matter as long as the frame/ subframe time is long enough to guarantee that the integrated power over the time meets the target.

The monotonic DAC used for controlling external DC-DC converters has a full scale current of 100  $\mu$ A and 9bits of resolution. The full scale can be increase by a factor of 2 to 200  $\mu$ A by setting regref\_setup[1]=1b.

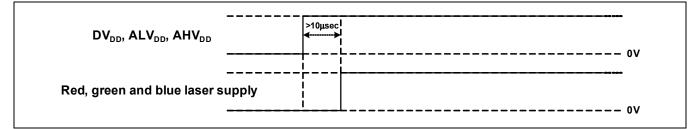

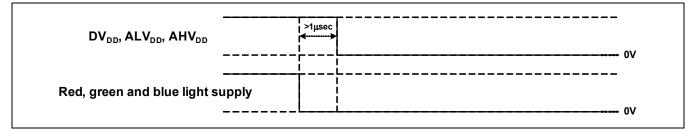

If the  $Ix_ON$  signals do not overlap and there is a significant amount of time (>10 µs) when  $Ix_ON=L$  (blanking period), opmode\_ctrl1[7] should be set to 1. In this case during the blanking period the DAC current is set to 0 and all the *IOUTx* signals are disconnected so that an external resistor divider network can be used to set the light sources anode voltage. The impedance level at *REGREF* pin, defined by R1//R2//input impedance of the DC-DC converter, should always be greater then 500 k $\Omega$ .

## 2.4 Timers

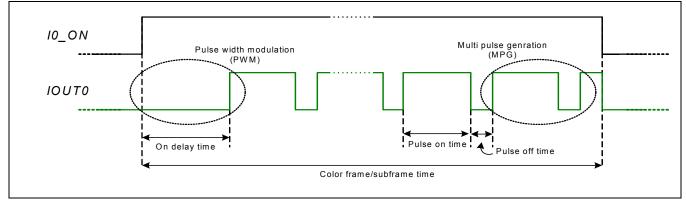

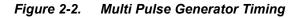

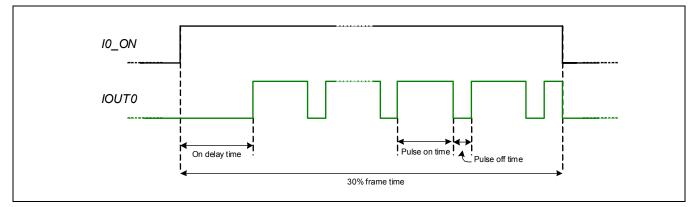

The M08888 features internal timers which allow an extra layer of control of the current by means of pulse width modulation (PWM) and multi pulse generation (MPG).

The clock source for the internal timer circuitry can be either the internal 25 MHz oscillator or an external clock fed through *CLK\_IN* (pin 23).

With reference to the following diagram for channel 0 (*I0\_ON, IOUT0*), PWM controls the "On delay time" while MPG adjusts independently both the "Pulse on time" and "Pulse off time".

Figure 2-1. Example of PWM and MPG Timers

24

Rev V4

### 2.4.1 Pulse Width Modulation (PWM)

Activating pulse width modulation will allow the output current to be delayed with respect to the  $Ix_ON$  signal. This may be useful if a blanking period is needed to allow the LCD or DLP to settle or it may be useful to save power if a laser is used and the same optical output can be achieved with fewer coulombs if higher laser driver currents and shorter durations are used (the coulombs will be less with higher current and shorter duration if the laser threshold current is approximately the same with PWM activated at higher current as it is at lower current without PWM activated).

PWM works in all optical power control modes: Open Loop, CPC and IPC.