# Core1553BBC MIL-STD-1553B Bus Controller DirectCore

# **Product Summary**

## **Intended Use**

- 1553B Bus Controller (BC)

- DMA Backend Interface to External Memory

## **Key Features**

- Supports MIL-STD-1553B

- Interfaces to External RAM

- Supports up to 128kbytes of Memory

- Synchronous or Asynchronous Backend Interface

- Backend Interface Identical to Core1553BRT

- Selectable Clock Rate of 12, 16, 20, or 24 MHz

- Provides Direct CPU Access to Memory

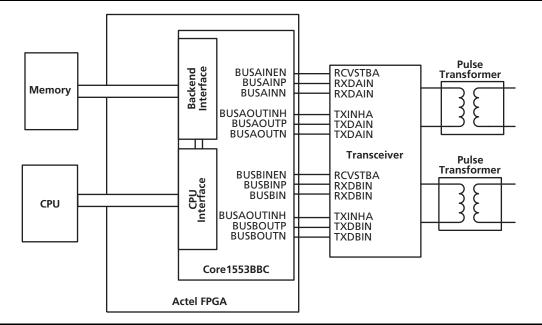

- Interfaces to Standard 1553B Transceivers

- Fully Automated Message Scheduling

- Frame Support

- Conditional Branching and Sub-routines

- Variable Inter-message Gaps and RT Response Times

- Real Time Clock for Message Scheduling

- Asynchronous Message Support

## **Supported Families**

- Fusion

- ProASIC3/E

- ProASIC<sup>PLUS</sup>

- Axcelerator

- RTAX

- SX-A

- RTSX-S

## **Core Deliverables**

- Netlist Version

- Compiled RTL Simulation Model, Compliant with the Actel Libero™ Integrated Design Environment (IDE)

- Compatible with the Actel Designer Place-and-Route Tool

- RTL Version

- VHDL or Verilog Core Source Code

- Synthesis Scripts

- Actel-Developed Testbenches, VHDL and Verilog

# Synthesis and Simulation Support

- Synthesis: Synplicity<sup>®</sup>, Synopsys<sup>®</sup> (Design Compiler<sup>®</sup>/ FPGA Compiler<sup>TM</sup>/FPGA Express<sup>TM</sup>), Exemplar<sup>TM</sup>

- Simulation: Vital-Compliant VHDL Simulators and OVI-Compliant Verilog Simulators

## **Verification and Compliance**

- Actel-Developed Simulation Testbench

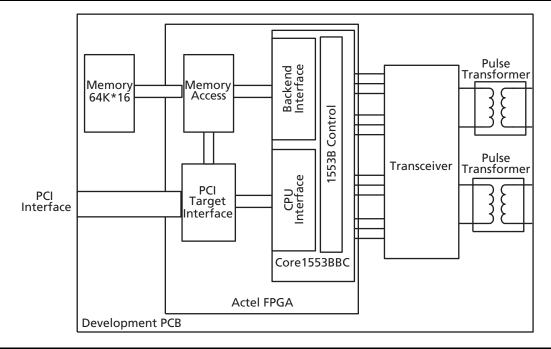

- Core Implemented on the 1553B BC Development System

- Third-Party 1553B Compliance Testing of the 1553B Encoder and Decoder Blocks Implemented in an A54SXA32-STD Device

## **Development System (Optional)**

- Complete 1553B BC Implementation in an SX-A

Device

- Includes a PCI Interface for Host CPU Connection

- Includes Transceivers and Bus Termination Components

### Contents

| General Description 2                     |

|-------------------------------------------|

| Core1553BBC Device Requirements 4         |

| Core1553BBC Verification and Compliance 4 |

| MIL-STD-1553B Bus Overview 4              |

| I/O Signal Descriptions 6                 |

| Bus Transceivers 20                       |

| Development System 20                     |

| Typical BC System 22                      |

| Specifications 24                         |

| Ordering Information 28                   |

| List of Changes 29                        |

| Datasheet Categories 29                   |

|                                           |

# **General Description**

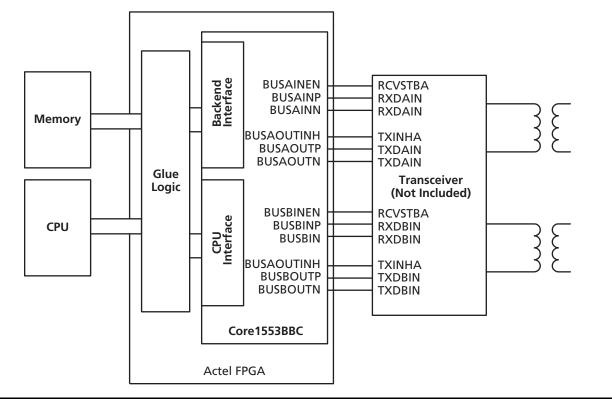

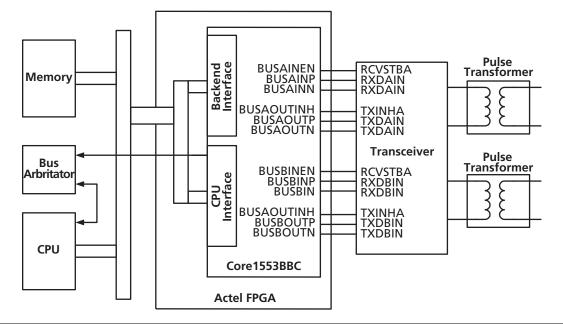

The Core1553BBC provides a complete, MIL-STD-1553B Bus Controller (BC). A typical system implementation using the Core1553BBC is shown in Figure 1.

Core1553BBC reads message descriptor blocks from the memory and generates messages that are transmitted on the 1553B bus. Data words are read from the memory

and transmitted on the 1553B bus. Data received is written to the memory. The core can be configured directly to connect to synchronous or asynchronous memory devices.

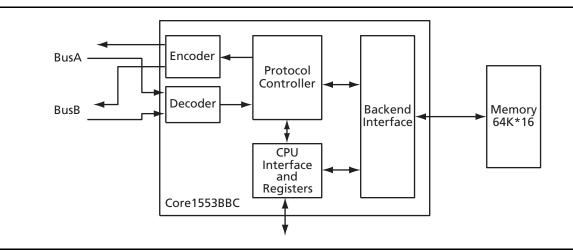

The core consists of five main blocks: the 1553B encoder, the 1553B decoder, a protocol controller block, a CPU interface, and a backend interface (Figure 2).

Figure 1 • Typical Core1553BBC System

Figure 2 • Core1553BBC BC Block Diagram

A single 1553B encoder takes each word to be transmitted and serializes it using Manchester encoding. The encoder includes independent logic to prevent the BC from transmitting for greater than the allowed period and to provide loopback fail logic. The loopback logic monitors the received data and verifies that the core has correctly received every word that is transmitted. The encoder output is gated with the bus enable signals to select which buses the RT should be transmitting.

Since the BC knows which bus is in use at any time, only a single decoder is required. The decoder takes the serial Manchester received data from the bus and extracts the received data words. The decoder requires a 12, 16, 20, or 24 MHz clock to extract the data and the clock from the serial stream.

The decoder contains a digital phased lock loop (PLL) that generates a recovery clock used to sample the incoming serial data. The data is then deserialized and the 16-bit word decoded. The decoder detects whether a command, status or data word has been received and checks that no Manchester encoding or parity errors occurred in the word.

The protocol controller block handles all the message sequencing and error recovery. This is a complex state machine that reads the 1553B message frames from the memory and transmits them on the 1553B bus.

The CPU interface allows the system CPU to access the control registers within the BC. It also allows the CPU to

directly access the memory connected to the backend interface. These features can simplify system design.

The backend interface for the Core1553BBC allows a simple connection to a memory device. The backend interface can be configured to connect to either synchronous or asynchronous memory devices. This allows the core to be connected to synchronous logic or memory within the FPGA or to external asynchronous memory blocks. The interface supports a standard bus request and grant protocol and provides a WAIT input, allowing the core to share system memory devices. This allows the core to share system memory rather than have its own dedicated memory block.

## **Core1553BBC Operation**

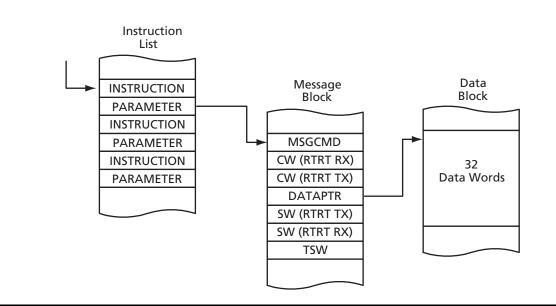

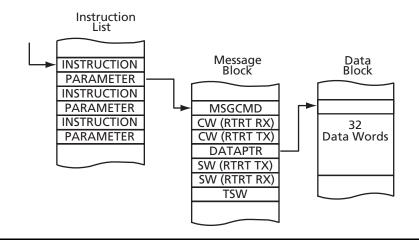

A bus controller is responsible for sending data bus commands, participating in data transfers, receiving status responses, and monitoring the bus system. The system CPU will create message lists in the BC memory, as illustrated in Figure 3.

When started, the BC works its way through the message lists. The Core1553B transmits the specified 1553B command and data words, and receives the 1553B status word and associated data words and writes them to the BC memory. During this process, the BC monitors all possible 1553B error conditions. If an RT does not respond correctly, the BC will retry the message on both the original bus and the alternate bus.

#### Figure 3 • Message Lists

# **Core1553BBC Device Requirements**

The Core1553BBC can be implemented in several Actel FPGA devices. Table 1 shows typical utilization figures for the Core1553BBC implemented in these devices.

#### Table 1Device Utilization

|                         | C             | ells or Tiles |       |               |             |

|-------------------------|---------------|---------------|-------|---------------|-------------|

| Family                  | Combinatorial | Sequential    | Total | Device        | Utilization |

| Fusion                  | 1773          | 558           | 2331  | AFS600        | 17%         |

| ProASIC3/E              | 1773          | 558           | 2331  | A3PE600       | 17%         |

| ProASIC <sup>PLUS</sup> | 2250          | 560           | 2810  | APA150-STD    | 46%         |

| Axcelerator             | 1072          | 584           | 1656  | AX500-STD     | 20%         |

| RTAX-S                  | 1072          | 584           | 1656  | RTAX250-STD   | 9%          |

| SX-A                    | 1115          | 589           | 1704  | A54SX32A-STD  | 56%         |

| RTSX-S                  | 1098          | 598           | 1696  | RT54SX32S-STD | 57%         |

The Core1553BBC clock rate can be programmed to 12, 16, 20, or 24 MHz. All Actel device families listed in Table 1 easily meet this performance requirement.

When implemented in ProASIC<sup>PLUS</sup> or Axcelerator devices, the Core1553BBC can connect directly to the internal FPGA memory blocks, eliminating the need for external memories.

# Core1553BBC Verification and Compliance

Core1553BBC is based upon the Actel Core1553BRT, which has been fully verified against the RT validation Test Plan (MIL-HDBK-1553A, Appendix A). This ensures that the 1553B encoders and decoders are fully compliant to the 1553B specification. The actual bus controller function has been extensively verified in both simulation and hardware. Core1553BBC has been implemented on an A54SX32A-STD part connected to external transceivers and memory.

# **MIL-STD-1553B Bus Overview**

The MIL-STD-1553B bus is a differential serial bus used in military and space equipment. It is comprised of multiple redundant bus connections and communicates at 1MB per second.

The bus has a single active bus controller (BC) and up to 31 remote terminals (RTs). The BC manages all data transfers on the bus using the command and status protocol. The bus controller initiates every transfer by sending a command word and data if required. The selected RT will respond with a status word and data if required.

The 1553B command word contains a five-bit RT address, a transmit or receive bit, a five-bit sub-address and a fivebit word count. This allows for 32 RTs on the bus. However, since RT address 31 is used to indicate a broadcast transfer, only 31 RTs may be connected. Each RT has 30 sub-addresses reserved for data transfers. The other two sub-addresses (0 and 31) are reserved for mode codes. Data transfers contain up to (32) 16-bit data words. Mode code command words are used for bus control functions such as synchronization.

# Message Types

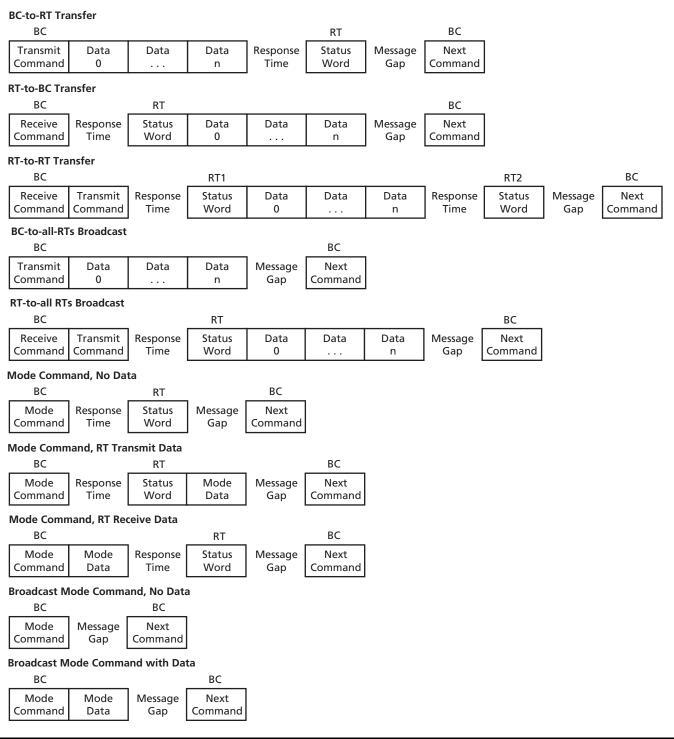

The 1553B bus supports ten message transfer types, allowing basic point-to-point and broadcast BC to RT data transfers, mode code messages, and direct RT-to-RT messages. Figure 4 shows the message formats.

Figure 4 • 1553B Message Formats

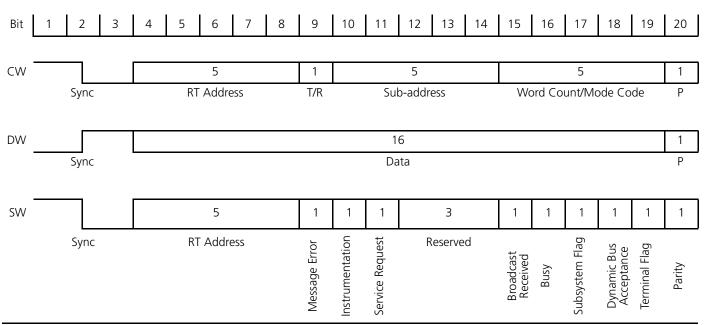

# Word Formats

There are only three types of words in a 1553B message: a command word (CW), a data word (DW), and a status word (SW). Each 20-bit word consists of a 3-bit sync pattern, 16 bits of data, and a parity bit (Figure 5).

Figure 5 • 1553B Word Formats

# **I/O Signal Descriptions**

#### Table 2 • 1553B Bus Interface

| Name      | Туре | Description                                                                       |  |

|-----------|------|-----------------------------------------------------------------------------------|--|

| BUSAINEN  | Out  | Active high output that enables for the A receiver                                |  |

| BUSAINP   | In   | Positive data input from the A receiver                                           |  |

| BUSAINN   | In   | Negative data input from the A receiver                                           |  |

| BUSBINEN  | Out  | Active high output that enables for the B receiver                                |  |

| BUSBINP   | In   | Positive data input from the bus to the B receiver                                |  |

| BUSBINN   | In   | Negative data input from the bus to the B receiver                                |  |

| BUSAOUTIN | Out  | Active high transmitter inhibit for the A transmitter                             |  |

| BUSAOUTP  | Out  | Positive data output to the bus A transmitter (is held high when no transmission) |  |

| BUSAOUTN  | Out  | Negative data output to the bus A transmitter (is held high when no transmission) |  |

| BUSBOUTIN | Out  | Active high transmitter inhibits the B transmitter                                |  |

| BUSBOUTP  | Out  | Positive data output to the bus B transmitter (is held high when no transmission) |  |

| BUSBOUTN  | Out  | Negative data output to the bus B transmitter (is held high when no transmission) |  |

| Name    | Туре | Description                                                                                                                                                                                                                                                                   |

|---------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK     | In   | Master clock input (either 12 MHz, 16 MHz, 20 MHz, or 24 MHz)                                                                                                                                                                                                                 |

| RSTINn  | In   | Reset input (active low)                                                                                                                                                                                                                                                      |

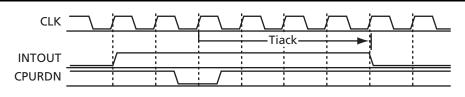

| INTOUT  | Out  | Interrupt Request (active high). The CPU is required to read the internal status register to find the reason for the interrupt. It is cleared by the CPU writing to the interrupt register.                                                                                   |

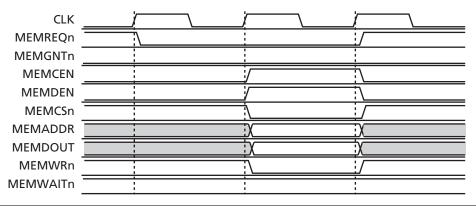

| MEMFAIL | Out  | This goes high if the core fails to read or write data to the backend interface within the required time. This can be caused by the backend not asserting MEMGNTn fast enough or asserting MEMWAITn for too long. It is cleared by the CPU writing to the interrupt register. |

| BUSY    | Out  | This is high when the core is active, i.e. processing a message list.                                                                                                                                                                                                         |

| EXTFLAG | In   | External flag input used by the condition codes within the bus controller                                                                                                                                                                                                     |

### Table 3Control and Status Signals

# **CPU Interface**

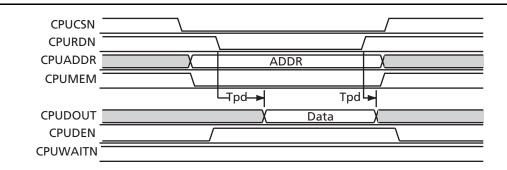

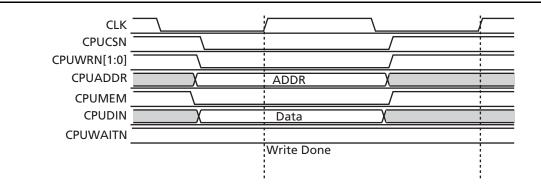

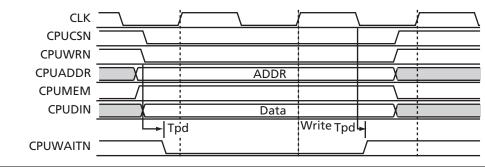

The CPU interface allows access to the Core1553BBC internal registers and direct access to the backend memory. This interface is synchronous to the clock (Table 4).

| Name          | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPUCSn        | In   | CPU chip select input (active low)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| CPUWRn[1:0]   | In   | CPU write input (active low). Two write inputs are provided for processors that support byte operations. When CPUWRn[1] is '0,' data bits [15:8] are written. When CPUWRn[0] is '0,' data bits [7:0] are written.                                                                                                                                                                                                                                                                                                                                                                                       |

| CPURDn        | In   | CPU read input (active low)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CPUWAITn      | Out  | CPU wait output (active low) indicates that the CPU should hold CPURDn or CPUWRn active while<br>the core completes the read or write operation. CPUWAITn is not asserted when the internal CPU<br>registers are accessed. When accessing the backend interface through the core, CPUWAIT will be<br>activated for a minimum of four clock cycles for read operations and three for write operations.<br>CPUWAITn is asserted for extra clock cycles if the backend interface delays asserting MEMGNTn or<br>asserts MEMWAITn.<br>Timing is shown in the Figure 12 on page 24 and Figure 13 on page 25. |

| CPUMEM        | In   | Selects whether the CPU accesses internal registers or backend memory.<br>'0': Accesses internal registers, register number is specified on CPUADDR[2:0]<br>'1': Accesses the backend memory                                                                                                                                                                                                                                                                                                                                                                                                            |

| CPUADDR[15:0] | In   | CPU address input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| CPUDOUT[15:0] | Out  | CPU data output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CPUDIN[15:0]  | In   | CPU data input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CPUDEN        | Out  | Data bus enable (active high). This signal is high when the core is providing data output on the CPUDOUT bus. It is intended for a tristate enable function.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

Table 4 • CPU Interface Signals

## Backend Interface

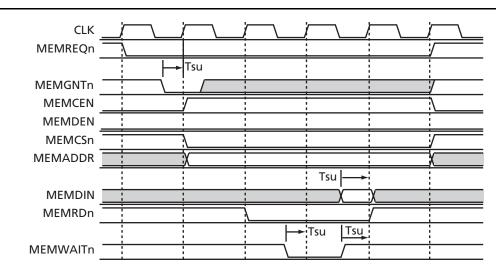

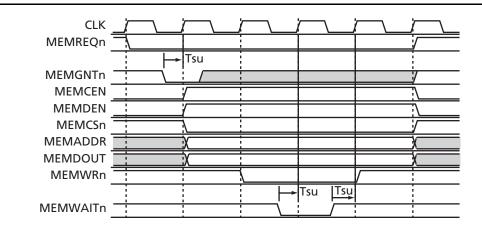

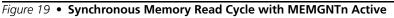

The backend interface supports both synchronous operation and asynchronous operation to backend devices. Synchronous operation directly supports the use of internal FPGA memory blocks. Asynchronous operation allows connection to standard external memory devices.

| Name          | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

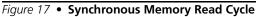

| MEMREQn       | Out  | Memory Request (active low) output. The BC holds MEMREQn active if it requires additional memory access cycles to take place immediately after the current memory cycle. This occurs during the intermessage gap.                                                                                                                                                                                                                                                                                                                                                                                             |

| MEMGNTn       | In   | Memory Grant (active low) input. This input should be synchronous to CLK and needs to meet the internal register setup time. This input may be held low if the core has continuous access to the RAM.                                                                                                                                                                                                                                                                                                                                                                                                         |

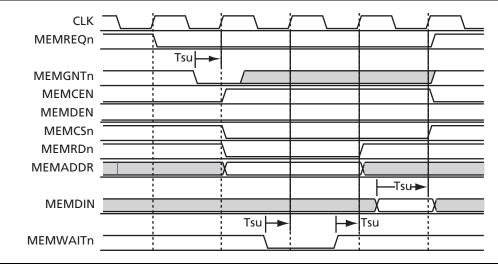

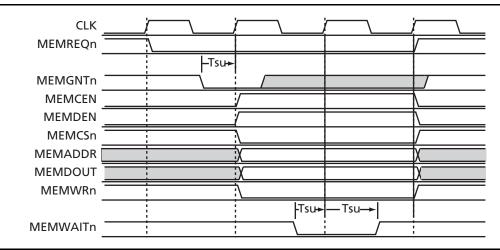

| MEMWRn[1:0]   | Out  | Memory Write (active low). When MEMWRn[1] is '0,' D[15:8] is written. When MEMWRn[0] is '0,' D[7:0] is written.<br>Synchronous mode: This output indicates that data will be written on the rising clock edge. If MEMWAITn is asserted, the MEMWRn pulse will be extended until MEMWAITn becomes inactive.<br>Asynchronous mode: This output will be low for a minimum of one clock period and can be extended by the MEMWAITn input. The address and data are valid one clock cycle before MEMWRn is active and held for one clock cycle after MEMWRn goes inactive.                                         |

| MEMRDn        | Out  | Memory Read (active low)<br>Synchronous mode: This output indicates that data is read on the next rising clock edge. If MEMWAITn is<br>active, then the data will be sampled on the rising clock edge on which MEMWAITn becomes inactive.<br>This signal is intended as the read signal for synchronous RAMS.<br>Asynchronous mode: This output will be low for a minimum of one clock period and can be extended by<br>the MEMWAITn input. The address is valid one clock cycle before MEMRDn is active and held for one<br>clock cycle after MEMRDn goes inactive. The data is sampled as MEMRDn goes high. |

| MEMCSn        | Out  | Memory Chip Select (active low). This output has the same timing as MEMADDR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| MEMWAITn      | In   | Memory Wait (active low) indicates that the backend is not ready, and the core should extend the read or write strobe period. This input should be synchronous to CLK and needs to meet the internal register setup time. It can be permanently held high.                                                                                                                                                                                                                                                                                                                                                    |

| MEMADDR[15:0] | Out  | Memory address output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| MEMDOUT[15:0] | Out  | Memory data output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| MEMDIN[15:0]  | In   | Memory data input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| MEMCEN        | Out  | Control signal enable (active high). This signal is high when the core is requesting the memory bus and has been granted control. It is intended to enable any tristate drivers that may be implemented on the memory control and address lines.                                                                                                                                                                                                                                                                                                                                                              |

| MEMDEN        | Out  | Data bus enable (active high). This signal is high when the core is requesting the memory bus has been granted control and is waiting to write data. It is intended to enable any bidirectional drivers that may be implemented on the memory data bus.                                                                                                                                                                                                                                                                                                                                                       |

Table 5 • Backend Signals

The backend interface must allow the bus controller access to the memory when requested. The memory access time from MEMREQn low to completion of the access cycle MEMRDn and MEMWRn high varies depending on the BC setup. When the CPU is allowed to access the memory through the bus controller

(CPUMEMEN active), the memory access time is reduced (Table 6 on page 9).

If the backend fails to allow the bus controller access to the memory in the required time, the bus controller will assert its MEMFAIL output and stop operation.

# **Miscellaneous I/O**

Several inputs are used to modify the core functionality to simplify integration in the application. These inputs should be tied to logic '0' or logic '1' as appropriate (Table 7).

| Table 6 • Me | mory Access | Requirements |

|--------------|-------------|--------------|

|--------------|-------------|--------------|

| CPUMEMEN | CLK Speed MHz | Memory Access Time |

|----------|---------------|--------------------|

| 0        | 12            | 9.58µs             |

| 0        | 16            | 9.68µs             |

| 0        | 20            | 9.75µs             |

| 0        | 24            | 9.79µs             |

| 1        | 12            | 4.58µs             |

| 1        | 16            | 4.68µs             |

| 1        | 20            | 4.75µs             |

| 1        | 24            | 4.79µs             |

### Table 7Miscellaneous I/O

| Name     | Туре | Description                                                                                                                                                                                                                                                       |

|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ASYNCIF  | In   | When '1,' the backend interface is in asynchronous mode. When '0,' the backend interface is in synchronous mode.                                                                                                                                                  |

| CPUMEMEN |      | When '1,' the CPU interface has access to the backend memory. When '0,' the CPU cannot access the backend memory through the core. This must be set to '0' if the core shares the CPU memory, i.e. the CPU and memory buses are connected to the same system bus. |

## **Bus Controller Registers**

The bus controller has nine internal registers used to control the bus controller operation and provide status information (Table 8).

| Address | Name     | Туре | Size                                                                                                                                                                                | Function                                                                                                                                                                                                                                    |

|---------|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 000     | CONTROL  | W    | [3:0]                                                                                                                                                                               | Allows the CPU to control the BC                                                                                                                                                                                                            |

| 000     | STATUS   | R    | [15:0]                                                                                                                                                                              | Provides status information                                                                                                                                                                                                                 |

| 001     | SETUP    | RW   | [15:0]                                                                                                                                                                              | BC setup register                                                                                                                                                                                                                           |

| 010     | LISTPTR  | RW   | [15:0]                                                                                                                                                                              | Current LISTPTR value. The address of the current instruction being executed. At the start of operation, the CPU should set this to the point at the first instruction. This value will automatically step through the BC instruction list. |

| 011     | MSGPTR   | R    | [15:0]                                                                                                                                                                              | Current MSGPTR value. Provides the address of the message block being processed.                                                                                                                                                            |

| 100     | CLOCK    | RW   | [15:0] BC internal clock value<br>This 16-bit value counts up at a 1µs, 4µs, 8µs, or 32µs rate. This giv<br>maximum timer value of 2 seconds. The CPU may directly load<br>counter. |                                                                                                                                                                                                                                             |

| 101     | ASYNCPTR | RW   | [15:0]                                                                                                                                                                              | Asynchronous list pointer<br>Provides a pointer to a list of messages that will be processed when<br>started by the ASYNC message list bit in the control register.                                                                         |

### Table 8• Bus Controller Registers

## Table 8•Bus Controller Registers

| Address | Name      | Туре | Size   | Function                                                                                                                                                                                                                                                                                                                                                |

|---------|-----------|------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 110     | STACKPTR  | RW   | [15:0] | BC stack pointer<br>This is the internal stack pointer register; it is used for the CALL and<br>RETURN instructions. When the bus controller is started, the STACKPTR<br>is set to FFFF. The upper eight bits are fixed to FF, and the lower eight<br>bits will count down and up. This allows up to 255 addresses to be<br>stored in the stack memory. |

| 111     | INTERRUPT | RW   | [15:0] | Interrupt Register                                                                                                                                                                                                                                                                                                                                      |

### Table 9 • Setup Register

| Bits  | Name      | Туре | Reset | Function                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------|-----------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15    | FORCEORUN | RW   | 0     | '1': If a BC-RT message with a word count between 1 and 31 is carried out, the BC will transmit for greater than 680μs. This will cause the transmitter timer to trigger and the BC to shutdown.<br>'0': Normal operation                                                                                                                                                                                               |

| 14    | CLOCKEN   | RW   | 0     | Enables the internal CLOCK to count<br>'0': Internal CLOCK will not count<br>'1': Internal CLOCK enabled<br>The clock is automatically enabled by the WAITC instruction.                                                                                                                                                                                                                                                |

| 13:12 | CLKFREQ   | RW   | 01    | Tells the core what the external clock frequency is<br>00: 12 MHz<br>01: 16 MHz<br>10: 20 MHz<br>11: 24 MHz                                                                                                                                                                                                                                                                                                             |

| 11    | RETRYMODE | WR   | 0     | Sets how the retry system works<br>'0': Retries on the same bus for the number of times set by the reties setting in the<br>message block, then on the alternate bus for the number of times set by the alternate<br>bus reties in the message block.<br>'1': Reties alternates between the two buses. The total number of retries is the number<br>of reties plus alternative bus retries as set in the message block. |

| 10    | INTENABLE | RW   | 0     | Enables the external interrupt pin<br>'1': The INTPENDING bit will drive the INTOUT pin<br>'0': The INTOUT pin is held at a '0'                                                                                                                                                                                                                                                                                         |

| 9     | AUTOCLOCK | RW   | 1     | '1': Sets the CLOCK register to 0000 when the BC is started<br>'0': The CLOCK register is not reset when the BC is started                                                                                                                                                                                                                                                                                              |

| 8     | AUTOSTACK | RW   | 1     | '1': Sets the STACKPTR register to FFFF when the BC is started<br>'0': The STACKPTR register is not reset when the BC is started. This allows the BC to be<br>restarted when previously stopped.                                                                                                                                                                                                                        |

| 7:6   | CLKRATE   | RW   | 00    | Sets the rate at which the TIMER and CLOCK count<br>00: 1μs<br>01: 4μs<br>10: 8μs<br>11: 32μs                                                                                                                                                                                                                                                                                                                           |

| 5:4   | IMG       | RW   | 00    | Sets the default minimum inter-message GAP<br>00: 4μs<br>01: 8μs<br>10: 16μs<br>11: 32μs<br><b>Note:</b> The actual inter-message GAP is a function of the memory access times. Typically,<br>six memory accesses need to take place in the inter-message gap.                                                                                                                                                          |

## Table 9 • Setup Register (Continued)

| Bits | Name     | Туре | Reset | Function                                                                                                         |

|------|----------|------|-------|------------------------------------------------------------------------------------------------------------------|

| 3:2  | RESPTIME | RW   | 01    | Sets the maximum time that the BC will wait for an RT to respond<br>00: 12μs<br>01: 16μs<br>10: 20μs<br>11: 24μs |

| 1:0  | Reserved | R    | 00    | Reserved, return 00                                                                                              |

### Table 10Control Register

| Bits | Name  | Туре | Function                                                                                                                                                                                                                                                                                                                                                     |

|------|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3    | ASYNC | W    | Writing a '1' causes the bus controller to jump to process the asynchronous instruction list pointed to by the ASYNCPTR register at the end of the current message. When a RETAS instruction is found, the bus controller returns to the original instruction list. An ASYNC instruction can be issued while the bus controller is both active and inactive. |

| 2    | ABORT | W    | Writing a '1' stops the bus controller immediately; both normal and asynchronous message operation will be aborted.                                                                                                                                                                                                                                          |

| 1    | STOP  | W    | Writing a '1' stops the bus controller at the end of the current message.                                                                                                                                                                                                                                                                                    |

| 0    | START | W    | Writing a '1' starts the bus controller. The bus controller cannot be started when an asynchronous message is active.                                                                                                                                                                                                                                        |

### Table 11Status Register

| Bits | Name     | Туре | Function                                                                                                                                              |

|------|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:8 | VERSION  | R    | Indicates the Core1553BBC code revision<br>Core release notes provide latest version numbers.                                                         |

| 7:6  | Reserved | R    | Reserved, set to 00                                                                                                                                   |

| 5    | LOOPFAIL | R    | Indicates that a loopback failure occurred in the current frame                                                                                       |

| 4    | FRAMEOK  | R    | Indicates that all the messages in the current frame have completed successfully and no system action is required                                     |

| 3    | FLAG     | R    | Indicates the value of the flag condition stored by the STOREFLAG instruction                                                                         |

| 2    | ASYNC    | R    | Asynchronous message requested or in progress. This bit is cleared by the RETAS instruction. When it is active, the bus controller cannot be started. |

| 1    | BUSINUSE | R    | Indicates which bus is in use<br>0: Bus A<br>1: Bus B                                                                                                 |

| 0    | ACTIVE   | R    | BC is Active                                                                                                                                          |

### Table 12Interrupt Register

| Bits | Name       | Туре | Fund                                                                                           | ction                                                                                                                                                                                                         |  |  |

|------|------------|------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 15   | INTPENDING | RW   | When set, the BC has an interrupt pending. This bit is set if any of the INTVECT bits are set. |                                                                                                                                                                                                               |  |  |

| 14:8 | INTVECT    | RW   |                                                                                                | rupt Reason<br>CPU writing a '1' to the bit clears the bit.                                                                                                                                                   |  |  |

|      |            |      | 14                                                                                             | BC has completed the message list, HALT instruction executed                                                                                                                                                  |  |  |

|      |            |      | 13                                                                                             | INTREQ instruction executed                                                                                                                                                                                   |  |  |

|      |            |      | 12                                                                                             | Memory access failure. This bit also directly drives the MEMFAIL output.                                                                                                                                      |  |  |

|      |            |      | 11 Asynchronous message is completed, RETAS instruction is executed.                           |                                                                                                                                                                                                               |  |  |

|      |            |      | 10                                                                                             | 10 Transmitter shutdown is set when the core detects that it has been transmitting continuous on the bus for greater than 700μs. When set, the BC disables its transmitter.                                   |  |  |

|      |            |      | 9                                                                                              | Stack pointer overflow or underflow is set if the BC attempts to push more than 256 return addresses onto the stack or pop of a non-existent address from the stack. The BC stops operation when this occurs. |  |  |

|      |            |      | 8                                                                                              | Corrupt instruction list or data table.<br>Illegal command written to the control register, e.g. start instruction while an asynchronous<br>message is active. The BC stops operation when this occurs.       |  |  |

| 7:0  | USERVECT   | R    | Provi                                                                                          | Provides the user-supplied interrupt reason as set by the instruction parameter                                                                                                                               |  |  |

## **Bus Controller Operation**

After power-up, the bus controller waits while the CPU sets up the bus controller memory and registers. The memory contains an instruction list, message blocks, and data blocks. Once the instruction list, message blocks, and data blocks are setup, the CPU starts the bus controller. The bus controller works its way through all the message blocks until it reaches the end of the instruction list (Figure 6).

The instruction list contains a list of pointers to message blocks. The message block contains the command words transmitted on the 1553B bus and status words received from the 1553B bus. It also contains a pointer to a data block. The data block contains the data transmitted on the 1553B bus, or the data received from the 1553B bus.

Figure 6 • BC Memory Usage

## Instruction List

The instruction list contains pairs of words: an instruction and a parameter. Core1553BBC supports a broad set of instructions allowing branching and sub-routine calls with condition code support. This allows complex instruction lists to be supported. The instruction contains a 4-bit OPCODE and a 5-bit condition code field (Table 13 and Table 14).

#### Table 13 • Instruction Word

| 15:13    | 12:8     | 7:4      | 3:0    |  |

|----------|----------|----------|--------|--|

| Reserved | CONDCODE | Reserved | OPCODE |  |

All of the OPCODES support the condition code field. If the condition is TRUE, then the OPCODE is carried out; otherwise, the BC continues to the next instruction. For RT-to-RT messages, the condition code will be true if the bit is set in either status word or not set in either status word (Table 15 on page 14).

| Table 14 • | Supported | Instructions |

|------------|-----------|--------------|

|------------|-----------|--------------|

| OPCODE | Function | <b>Condition Code</b> | Parameter                                  | Description                                                               |

|--------|----------|-----------------------|--------------------------------------------|---------------------------------------------------------------------------|

| 0000   | NOP      | N/A                   | N/A                                        | No operation, jumps to next message                                       |

| 0001   | DOMSG    | Yes                   | Message Block Address                      | Process the message block                                                 |

| 0010   | JUMP     | Yes                   | New Instruction Address                    | Jumps to the new message list address                                     |

| 0011   | INTR     | Yes                   | User interrupt value<br>(Lower eight bits) | Force a BC interrupt                                                      |

| 0100   | HALT     | Yes                   | User interrupt value<br>(Lower eight bits) | Stop the BC                                                               |

| 0101   | DELAY    | Yes                   | Timer value<br>(Lower eight bits)          | Loads the timer with the parameter and waits until the timer reaches zero |

| OPCODE | Function | <b>Condition Code</b> | Parameter               | Description                                                                                                                                                              |

|--------|----------|-----------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0110   | LOADC    | Yes                   | Clock value             | Loads the BC clock                                                                                                                                                       |

| 0111   | WAITC    | Yes                   | Clock value             | Waits until the BC clock reaches the specified value                                                                                                                     |

| 1000   | CALL     | Yes                   | New Instruction Address | Jumps to the new message list address and pushes the return address onto the stack                                                                                       |

| 1001   | RET      | Yes                   | N/A                     | Gets a return instruction address from the stack and jumps to it                                                                                                         |

| 1010   | RETAS    | Yes                   | N/A                     | Gets a return instruction address from the stack and jumps to<br>it. Also clears the ASYNC bit in the status register allowing<br>further ASYNC messages to be accepted. |

| 1011   | STOREF   | Yes                   | N/A                     | Stores the selected flag so that it may be tested at a later stage.<br>The condition code field indicates which flag to store.                                           |

| Others | Illegal  | N/A                   | N/A                     | Will halt operation and set the illegal OPCODE interrupt                                                                                                                 |

## Table 14 • Supported Instructions (Continued)

### Table 15 • Condition Codes

| <b>Condition Code</b> | Function | Description                                                                                                                                                         |  |  |  |

|-----------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 00000                 | ALWAYS   | Always perform the associated instruction                                                                                                                           |  |  |  |

| 00001                 | RESP     | Performs the instruction if there was a response to the previous message                                                                                            |  |  |  |

| 00010                 | GBR      | Performs the instruction if the previous message was successful                                                                                                     |  |  |  |

| 00011                 | TF       | Performs the instruction if the Terminal Flag was set in the last received status word                                                                              |  |  |  |

| 00100                 | DBA      | Perform the instruction if the Dynamic Bus Acceptance flag was set in the last received status word                                                                 |  |  |  |

| 00101                 | SSF      | Performs the instruction if the Sub-system Flag was set in the last received status word                                                                            |  |  |  |

| 00110                 | BUSY     | Performs the instruction if the Busy bit was set in the last received status word                                                                                   |  |  |  |

| 00111                 | BR       | Performs the instruction if the Broadcast Received bit was set in the last received status word                                                                     |  |  |  |

| 01000                 | SR       | Performs the instruction if the Service Request bit was set in the last received status word                                                                        |  |  |  |

| 01001                 | ME       | Performs the instruction if the Message Error bit was set in the last received status word                                                                          |  |  |  |

| 01010                 | SWE      | Performs the instruction if the RT address field is incorrect, the instrumentation bit is set, or any of the reserved bits was set in the last received status word |  |  |  |

| 01011                 | SWAB     | Performs the instruction if any bits are set in the last received status word (ignoring the RT address field)                                                       |  |  |  |

| 01100                 | ASYNC    | Performs the instruction if asynchronous message processing is active                                                                                               |  |  |  |

| 01101                 | EXT      | Performs the instruction if the External flag input is active '1'                                                                                                   |  |  |  |

| 01110                 | SFLAG    | Performs the instruction if the previously stored flag bit was set                                                                                                  |  |  |  |

| 10000                 | NEVER    | Never performs the associated instruction                                                                                                                           |  |  |  |

| 10001                 | NORESP   | Performs the instruction if there was no response to the previous message                                                                                           |  |  |  |

| 10010                 | NGBR     | Performs the instruction if the previous message was unsuccessful                                                                                                   |  |  |  |

| 10011                 | NTF      | Performs the instruction if the Terminal Flag was not set in the last received status word                                                                          |  |  |  |

| 10100                 | NDBA     | Performs the instruction if the Dynamic Bus Acceptance flag was not set in the last received status word                                                            |  |  |  |

| 10101                 | NSSF     | Performs the instruction if the Sub-System Flag was not set in the last received status word                                                                        |  |  |  |

| 10110                 | NBUSY    | Performs the instruction if the Busy bit was not set in the last received status word                                                                               |  |  |  |

| <b>Condition Code</b> | Function | Description                                                                                                                                                                |

|-----------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10111                 | NBR      | Performs the instruction if the Broadcast Received bit was not set in the last received status word                                                                        |

| 11000                 | NSR      | Performs the instruction if the Service Request bit was not set in the last received status word                                                                           |

| 11001                 | NME      | Performs the instruction if the Message Error bit was not set in the last received status word                                                                             |

| 11010                 | NSWE     | Performs the instruction if the RT address field is correct and the instrumentation bit is not set, and none of the reserved bits are set in the last received status word |

| 11011                 | NOSWAB   | Performs the instruction if no bits (ignoring the RT address field) are set in the last received status word                                                               |

| 11100                 | NASYNC   | Performs the instruction if asynchronous message processing is not active                                                                                                  |

| 11101                 | NEXT     | Performs the instruction if the External flag input is inactive '0'                                                                                                        |

| 11110                 | NSFLAG   | Performs the instruction if the previously stored flag bit was not set                                                                                                     |

| Others 0xxxx          | Illegal  | Equivalent to NEVER                                                                                                                                                        |

| Others 1xxxx          | Illegal  | Equivalent to ALWAYS                                                                                                                                                       |

## Table 15• Condition Codes (Continued)

# **Message Block**

An 8-word message block controls each message. The BC reads the 1553B command words from the message block and will write the received status words back to message block. Message blocks must be positioned on an 8-word memory boundary (Table 16).

| Offset | Contents   | Written by        | Description                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            |                                                                                |  |  |  |

|--------|------------|-------------------|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------------|--|--|--|

| 0      | MSGCMD     | CPU               | Type of 1553B N                                                                                                        | Type of 1553B Message                                                                                                                                                                                                                                                                                                                                                                                                                           |                            |                                                                                |  |  |  |

|        |            |                   | 15:10                                                                                                                  | Inter-message GAP (IMG) after this message, 0 to 63µs.<br>When 000000, it uses the inter-message gap as set by the BC setup register.<br>Longer IMG values can be achieved by using the DELAY instruction between<br>messages.<br>The actual IMG may be llonger than when set by this register. The BC needs<br>to perform up to six memory accesses during the IMG period. If the backend<br>memory responds slowly, then the IMG may increase |                            |                                                                                |  |  |  |

|        |            |                   | 9                                                                                                                      | '1': The CL                                                                                                                                                                                                                                                                                                                                                                                                                                     |                            | at the mid-point of the data word sync is used as the ize with data mode code. |  |  |  |

|        |            |                   | 8:                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            |                                                                                |  |  |  |

|        |            |                   | 7:6                                                                                                                    | Retries on                                                                                                                                                                                                                                                                                                                                                                                                                                      | es on Alternate Bus 0 to 3 |                                                                                |  |  |  |

|        |            |                   | 5:4                                                                                                                    | Retries on                                                                                                                                                                                                                                                                                                                                                                                                                                      | Retries on Bus 0 to 3      |                                                                                |  |  |  |

|        |            |                   | 3:0                                                                                                                    | 0000                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                          | BC-to-RT                                                                       |  |  |  |

|        |            |                   |                                                                                                                        | 0001                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                          | RT-to-BC                                                                       |  |  |  |

|        |            |                   |                                                                                                                        | 0110                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6                          | Mode Code with no data                                                         |  |  |  |

|        |            |                   |                                                                                                                        | 0010                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2                          | Mode Code RT RX with data                                                      |  |  |  |

|        |            |                   |                                                                                                                        | 0011                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3                          | Mode Code RT TX with data                                                      |  |  |  |

|        |            |                   |                                                                                                                        | 0101                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5                          | RT-to-RT                                                                       |  |  |  |

|        |            |                   |                                                                                                                        | 1000                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8                          | Broadcast BC-to-RT                                                             |  |  |  |

|        |            |                   |                                                                                                                        | 1110                                                                                                                                                                                                                                                                                                                                                                                                                                            | E                          | Broadcast Mode Code RT with no data                                            |  |  |  |

|        |            |                   |                                                                                                                        | 1010                                                                                                                                                                                                                                                                                                                                                                                                                                            | А                          | Broadcast Mode Code RX with data                                               |  |  |  |

|        |            |                   |                                                                                                                        | 1101                                                                                                                                                                                                                                                                                                                                                                                                                                            | D                          | Broadcast RT-to-RT                                                             |  |  |  |

|        |            |                   |                                                                                                                        | Others                                                                                                                                                                                                                                                                                                                                                                                                                                          | Illegal                    |                                                                                |  |  |  |