# **Cyclone III Design Guidelines**

AN-466-2.2 Application Note

This document summarizes the various aspects of the Cyclone III device, and highlights the Quartus<sup>®</sup> II software features that you should consider when you are designing with the Cyclone III devices. With good design practice and clear understanding of the design flow of the Cyclone III device, your design flow will be much easier.

This document covers the following topics:

- "Device Selection" on page 1

- "Early System Planning" on page 3

- "Board Design Considerations" on page 16

- "Design and Compilation" on page 28

- "Verification" on page 45

- "Design Debugging" on page 56

- "Testing" on page 56

- "Other Considerations" on page 57

## **Device Selection**

This section provides the information for you to consider when selecting a Cyclone III device for your system.

#### **Device Feature Consideration**

The Cyclone III device family offers from over 5,000 logic elements (LEs) to nearly 120,000 LEs and is suitable for a wide range of applications.

Always choose a device that has more LEs than the estimated count for your design requirements:

- You will have extra LEs if you want to upgrade or expand your design.

- Consider having additional LEs and memories for debugging purposes.

- Additional resources allow more flexibility with the Quartus II software for optimizing placement and routing for maximum performance, lower power consumption or both.

- For the number of LEs and other resource counts of the Cyclone III devices, refer to the Cyclone III Device Family Overview chapter in the Cyclone III Device Handbook.

© 2013 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

**Device Selection** Page 2

## I/O Pin Count, Package Offering and Vertical Migration

The Cyclone III device family offers up to a maximum of 535 user I/O pins.

Depending on your application and board layout, you can select the available package options:

- Quad Flat Pack (QFP)

- FineLine Ball Grid Array (FBGA) with a 1.0 mm ball pitch

- Ultra FBGA package (UBGA) with an 0.8 mm ball pitch—the smallest in the Cyclone III device family and saves board space.

Cyclone III devices support vertical migration within the same package. For a given package, the devices across different densities have the same locations for the power pins, configuration pins and dedicated pins. This allows future upgrade or changes to your Cyclone III design without having to change the board layout as you can replace the Cyclone III device in your board with another Cyclone III device of a different density.

For best results, you can specify the migration device before compiling your initial design with the Quartus II software to ensure that only pins that are available in the same locations on both devices are used in the design for seamless migration to a larger or smaller device.

The number of differential channels may vary across device density.

For more information about the number of differential channels available for different densities and packages of the Cyclone III device family, refer to the *High-Speed* Differential Interfaces in the Cyclone III Device Family chapter in the Cyclone III Device Handbook.

# **Speed Grade**

Device speed grade affects the timing closure of the device. Depending on the density and package, Cyclone III devices are available in three different speed grades:

- -6 (fastest),

- –7 and,

- **-**8

When migrating to a device of different speed grade, check the timing report from the timing analysis to ensure that there is no timing violation between different blocks within the Cyclone III device, between the Cyclone III device and other devices on the board.

Always design with a sufficient timing margin so that your design can work on devices of different speed grades. Generally, the difference of one speed grade can mean a core  $f_{MAX}$  or I/O performance difference of up to 20%.

**Early System Planning** Page 3

# **Early System Planning**

It is important to know your system requirement and what your Cyclone III device can offer at the early stage of the design cycle.

## **Early Power Estimation**

As FPGAs have increased in logic capacity and performance, the power consumption must be accurately estimated for appropriate power supply, decoupling and thermal solution planning. The power supply must be able to provide enough current for the device operation and the thermal solution must be able to cool the device junction temperature to within the specification.

Altera provides a power estimation tool called the Early Power Estimator (EPE) to help you estimate the power consumption of your design during the system planning phase. The EPE allows you to estimate the power consumption, current drawn from the power supply and device junction temperature based on the device resources that you are going to use in your design, along with the information about the ambient temperature, heat sink, air flow and board thermal model.

You can either enter the design information manually into the spreadsheet or import a power estimator file of a fully or partially completed design from the Quartus II software. After importing a file, you can edit some of the input parameters such as the ambient temperature, airflow, clock frequency and toggle percentage to suit your system requirements.

For more information about the EPE and ways generate and import the power estimator file, refer to the PowerPlay Early Power Estimator User Guide for Cyclone III FPGAs.

# I/O Support

This section discusses the general Cyclone III device I/O support. Before starting with the I/O planning, take some time to review the support offered by the Cyclone III I/Os.

### Selectable I/O Standards

Cyclone III devices support a wide range of industry I/O standards, including single-ended, voltage-referenced and differential I/O standards. Selection factors are driven by performance versus cost. Table 1 simplifies the selection choice for each I/O signaling type.

Page 4 Early System Planning

Table 1. Selection Criteria for Each I/O Signaling Type

| I/O Signaling Type                                                     | Selection Criteria                                                                                                                                                                                                                                                       |                                                                                                                                                         |  |

|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| I/O Signaling Type                                                     | Performance                                                                                                                                                                                                                                                              | Cost                                                                                                                                                    |  |

| Single-ended                                                           | Slow speed rail-to-rail interface, limited by large voltage swing and noise.                                                                                                                                                                                             | Fairly low, unless reflection causes signal integrity concerns, whereby termination is required.                                                        |  |

| Voltage-reference<br>(single-ended and<br>differential) <sup>(1)</sup> | Reduced Simultaneous Switching Output (SSO) effects from large number of pins changing levels at the same time. Improved logic transition rate with reduced voltage swing and minimized noise caused by reflections due to termination requirements of the I/O standard. | High, with extra components due to termination requirement and additional clean reference voltage, $V_{TT}$ .                                           |  |

| Differential (2), (3)                                                  | Superior speed (up to 840 Mbps), lower swing voltage and increased noise immunity with common mode noise rejection capability.                                                                                                                                           | Low, with reduced physical traces and I/O resources by implementing serialization/deserialization (SERDES) logic to replace parallel data transmission. |  |

#### Notes to Table 1:

- (1) Differential voltage-referenced standards can only be used for clocking. These I/O standards are only supported on the GCLK and PLL\_OUT pins.

- (2) Side I/O banks support dedicated differential buffers. Top and bottom I/O banks support differential signaling with an additional resistor network on the transmitter side.

- (3) For details on the guidelines and considerations of the high-speed **LVDS** interface implementation in a Cyclone III device, refer to *AN 479: Design Guidelines for Implementing LVDS Interfaces in Cyclone Series Devices.*

### Flexible I/O Banks

Simultaneous support of various I/O standards is possible with efficient I/O groupings in banks. Each bank must be supplied with one  $V_{CCIO}$  level. Each I/O bank is powered up individually by the VCCIO pins of that particular bank and is independent of the  $V_{CCIO}$  of other I/O banks. Eight I/O banks are offered for increased flexibility to be used with multi-voltage systems.

An output buffer does not meet the configured I/O standard specification if the  $V_{CCIO}$  is out of the recommended operating range specified in the Cyclone III device datasheet for the I/O standard.

Although there can only be one V<sub>CCIO</sub> voltage per I/O bank, Cyclone III devices permit additional input signaling capabilities.

For more information about the acceptable input and output levels, refer to the *I/O Features in the Cyclone III Device Family* chapter in the *Cyclone III Device Handbook*.

Each Cyclone III I/O bank has a VREF bus to accommodate voltage-referenced I/O standards. Multiple VREF pins within an I/O bank feed the common VREF bus. Each bank can only have a single  $V_{CCIO}$  voltage level and a single  $V_{REF}$  voltage level at a given time.  $V_{REF}$  is used as a reference voltage for voltage-referenced inputs (SSTL and HSTL I/O standards) to determine logic threshold. Because of this, it is important for VREF to be noise-free.

Follow pad placement guidelines in the *I/O Features in the Cyclone III Device Family* chapter in the *Cyclone III Device Handbook* to minimize noise coupling onto the reference voltage.

Early System Planning Page 5

Voltage deviation on the VREF pin can affect the threshold sensitivity for the input operation. If a voltage referenced input is not utilized for a  $V_{REF}$  group, the VREF pin is released automatically by the Quartus II software for use as an I/O pin.

However, if the VREF pin is used as an I/O pin, it will have a higher pin capacitance due to the power bus loading effects. The I/O edge rate will be slower than regular I/O pins, which can affect the timing of the signal. For best results, do not use VREF pins as I/O pins when the VREF pins are part of a common bus or pin group that requires similar timing characteristics. Similarly, do not use the VREF pins for clocks.

### **External Memory Interface**

Cyclone III devices support interfaces to the DDR2 SDRAM, DDR SDRAM, and QDRII SRAM. Depending on device density and package, specific side of I/O bank may support up to x36 mode of memory interface. Supported modes in the Cyclone III devices are x8, x9, x16, x18, x32, and x36 modes. Use the Pin Planner tool to assist you in determining and making pin assignments for the memory interface.

In general, choose the top or bottom I/O banks instead of the side I/O banks to achieve a higher clock rate for the external memory interfaces. The Cyclone III devices support external memory interfaces up to 200 MHz.

- For more information about the DDR/DDR2 and QDRII pads placement, refer to the *Cyclone III Device I/O Feature* chapter in the *Cyclone III Device Handbook*.

- For more information about the recommended design flow to implement the DDR2 SDRAM memory interface with Cyclone III devices, refer to External Memory Interface Handbook Volume 5, Section I. ALTMEMPHY Design.

- For a complete table of the maximum clock rate support across all speed grades for every memory standard, refer to the External Memory Interfaces in the Cyclone III Device Family chapter in the Cyclone III Device Handbook.

### **Pin-Out Files**

The Cyclone III pin-out files contain information about the location for all the pins of the devices, according to package:

- For the I/O pins, you can find out which I/O bank and the V<sub>REF</sub> group the pins belong to.

- The pin-out files contain the description for the dedicated and multi-purpose pins.

- The pin-out files help designer to determine the I/O pins to be used when creating the design as well as when designing the board.

Apart from I/O pins, the location of dedicated and multi-purpose pins is also important during the board design stage.

To obtain device pin-outs for Cyclone III devices, refer to the *Device Pin-Outs* page of the *Literature* section of the Altera website (www.altera.com).

Page 6 Early System Planning

## **Planning and Selecting Configuration Scheme**

Select your device configuration method early to allow system and board designers to determine if any additional devices are required for your system. Your board layout depends on the configuration method that you plan to use for the programmable device, because different schemes require different connections. For board design guidelines related to configuration pins, refer to "Board Design Considerations" on page 16.

Cyclone III devices offer configuration data decompression and real-time remote system upgrades to save configuration memory space and time. Support for these configuration features varies depending on your configuration scheme.

Cyclone III devices also include optional configuration pins and a reconfiguration option that you must determine at the start and set up in the Quartus II software, so that you have all the information required for your board and system design. For the Quartus II software settings and pins related to the configuration options that affect your board and system design, refer to "Design and Compilation" on page 28.

Depending on the device densities and package options, you can configure Cyclone III devices using one of the following five configuration schemes:

- Active serial (AS)

- Active parallel (AP)

- Passive serial (PS)

- Fast passive parallel (FPP)

- Joint Test Action Group (JTAG)

A selection of configuration scheme with different configuration voltage standards is selected by driving the Cyclone III device's MSEL pins either high or low. Depending on the MSEL pin settings, you can either select a fast power-on reset (POR) time or a standard POR time. The fast POR time supports fast wake-up time applications, where it may be necessary for a device to wake up quickly to begin operation.

In Cyclone III devices, the supported configuration schemes differ for different device densities and package options. For example, the EP3C16 device's E144 package offers the AS, PS, and JTAG schemes while its U484 package offers the AS, PS, FPP, AP, and JTAG schemes.

- For more information about the supported configuration schemes, refer to the Cyclone III devices' Configuration Center on the Altera website.

- For complete information about the following items, refer to the *Configuration*, *Design Security*, *and Remote System Upgrades* in the Cyclone III Device Family chapter in the *Cyclone III Device Handbook*:

- Supported configuration schemes across device densities and package options

- Configuration voltage standards and POR time

- Methods to execute the required configuration schemes and all the necessary option pin settings, including the MSEL pin settings

Early System Planning Page 7

For new user of Altera device configuration schemes, the available choice of configuration schemes and methods in which the configuration schemes can be set up may be overwhelming. In general, Altera configuration schemes are categorized into the following configuration schemes:

- Active configuration scheme—provides a one-chip solution configuration to build a simple system, where only a serial configuration device is required for the AS configuration scheme or a parallel flash memory for the AP configuration scheme.

- Passive configuration scheme—provides a two-chip solution configuration. If your system already contains an external intelligent host or a microprocessor, you can utilize it with a flash memory to perform the passive configuration scheme such as the PS or FPP.

For more information on the configuration scheme selection, refer to the Configuration Center on the Altera website. This web page includes a link to the configuration guidelines that provide an overview of Altera FPGA configuration schemes and a general comparison of the schemes to guide you in choosing the one that best suits your design requirements.

All configuration schemes use a configuration device, a download cable or an external controller (for example, a  $MAX^{®}$  II device or microprocessor):

- The AS and AP schemes use an external flash memory, such as serial configuration device or a supported flash memory, respectively.

- The PS and JTAG schemes use either an external controller or a download cable.

- The FPP scheme uses an external controller.

When choosing the configuration scheme that best suits your system requirements, you may also want to consider the configuration time. Configuration time varies for different configuration schemes and depends on the configuration file size, configuration data width, frequency of the driving clock, and flash access time.

The AP configuration scheme offers the fastest configuration time among the supported configuration schemes in a Cyclone III device. The speedup in the configuration time is mainly due to the 16-bit wide parallel data bus which is used to retrieve data from the flash. However, a 24-bit address bus is required to connect the Cyclone III device to the address bus of the flash memory. In other words, 40 pins of your Cyclone III device and the flash memory would be occupied for the address bus and data transfer.

Comparatively, the FPP takes only 8 pins of your Cyclone III device and the flash memory device for the data transfer and does not require an address bus. Although the configuration of the FPP is not relatively as fast as the configuration of the AP, this scheme provides faster configuration time compared to any serial configuration scheme such as the AS and PS.

For the active configuration schemes such as the AS and AP, the DCLK is an output from the Cyclone III device that provides the timing for the configuration interface. The maximum DCLK frequency for the AS and AP is 40 MHz.

Page 8 Early System Planning

In the PS and FPP configuration, the DCLK is the clock input that is used to clock data from an external source into the target Cyclone III device. Data is latched into the device on the rising edge of the DCLK. In other words, you are able to monitor the DCLK frequency to control the configuration time in the passive configuration scheme by varying the clock from the external source. For the PS configuration, the maximum DCLK frequency is 133 MHz and for the FPP configuration, the maximum DCLK frequency is 100 MHz.

Table 2 simplifies the general comparison of the supported configuration schemes in Cyclone III.

Table 2. General Comparison for Supported Configuration Schemes in Cyclone III

| Configuration<br>Scheme      | Serial/Parallel<br>Configuration | Configuration<br>Method                          | Width of<br>Data bus<br>(in bits) | Width of<br>Address bus<br>(in bits) | Relative<br>configuration<br>time | Supported configuration feature         |

|------------------------------|----------------------------------|--------------------------------------------------|-----------------------------------|--------------------------------------|-----------------------------------|-----------------------------------------|

| Active Serial<br>(AS)        | Serial                           | Serial Configuration (EPCS) device               | 1                                 | _                                    | Moderate                          | Decompression, Remote<br>System Upgrade |

| Active Parallel (AP)         | Parallel                         | Supported parallel flash memory                  | 16                                | 24                                   | Fast                              | Remote System Upgrade                   |

|                              | Serial                           | Download cable                                   | 1                                 | _                                    | Moderate                          | Decompression                           |

| Passive Serial<br>(PS)       |                                  | MAX II or<br>microprocessor<br>with flash memory | 1                                 | _                                    | Moderate                          | Decompression                           |

| Fast Passive<br>Serial (FPP) | Parallel                         | MAX II or<br>microprocessor<br>with flash memory | 8                                 | _                                    | Fast                              | _                                       |

| (JTAG)                       | Serial                           | Download cable                                   | 1                                 | _                                    | Slow                              | _                                       |

|                              |                                  | Microprocessor with flash memory                 | 1                                 | _                                    | Slow                              | _                                       |

### **Configuration Devices**

You can use the Altera's serial configuration devices (EPCS) in the AS configuration scheme. Supported commodity parallel flash families are used in the AP configuration scheme. Check whether the configuration device supports the configuration bitstream file size of your Cyclone III device. In the PS and FPP configuration schemes, you can use a MAX II device or a microprocessor with a flash memory configuration method. In the AS and PS configuration schemes, you can use the compression feature to reduce the configuration file size of a large Cyclone III device.

For more information on the supported families for the commodity parallel flash, refer to the *Configuration*, *Design Security*, and *Remote System Upgrades* in the Cyclone III Device Family chapter in the *Cyclone III Device Handbook*.

**Early System Planning** Page 9

#### **Download Cables**

The Quartus II programmer supports configuring Cyclone III devices directly using PS or JTAG interfaces via Altera programming download cables. You can download design changes directly to the device with the Altera download cables, making prototyping easy and enabling you to make multiple design iterations in quick succession. You can use the same download cable to program configuration devices on the board and use JTAG debugging tools such as the SignalTap<sup>®</sup> II Logic Analyzer.

For more information about using Altera's download cables, refer to the following documents:

- USB-Blaster Download Cable User Guide

- ByteBlaster II Download Cable User Guide

- EthernetBlaster Communications Cable User Guide

#### Serial FlashLoader

When you use an AS configuration scheme, the conventional method to program an EPCS device is via the active serial (AS) programming interface.

However, with the Serial FlashLoader (SFL), you can program the EPCS device in-system via the JTAG interface. The SFL solution reduces the effort to have a separate programming interface for the Cyclone III and EPCS device because you are able to configure the Cyclone III and EPCS device using the same JTAG interface.

The SFL for the Cyclone III device is available with the Quartus II software, version 7.1 and higher. SFL Megafunction is available with the Quartus II software, version 6.0 and higher.

For more information about the SFL, refer to AN 370: Using the Serial FlashLoader with the Quartus II Software.

#### **MAX II Parallel Flash Loader**

If your system already contains the common flash interface (CFI) flash memory, you can use it for the Cyclone III device configuration storage as well. The parallel flash loader (PFL) feature with MAX II devices allows you to program the CFI flash memory devices through the JTAG interface. It also provides the logic to control the configuration from the flash memory device to the Cyclone III device and supports compression to reduce the size of your configuration data.

Both the PS and FPP configuration modes are supported using the PFL feature. If you choose this configuration method, you should check the list of supported flash devices early in your system design cycle and plan accordingly.

For more information about the MAX II PFL, refer to Parallel Flash Loader Megafunction User Guide.

Page 10 **Early System Planning**

#### **FPGA-Based Parallel Flash Loader**

The AP configuration scheme configures the Cyclone III device using the Intel StrataFlash® Embedded Memory P30 flash family and the Intel StrataFlash Embedded Memory P33 flash family, which are two industry standard flash families.

If your system contains a parallel flash device, you can use it to store configuration data. The parallel flash device reduces the configuration time through the parallel interface and provides a higher memory capacity to store configuration data. However, the parallel flash device does not support direct device programming through JTAG.

Using the FPGA-based PFL, you can use the Cyclone III JTAG interface to perform in-system programming for the parallel flash device. The PFL enables you to program the flash device indirectly before configuring the Cyclone III with the AP configuration scheme.

For more information about the FPGA-based PFL, refer to AN 478: Using FPGA-Based Parallel Flash Loader with the Quartus II Software.

## **Configuration Features**

This section describes the Cyclone III device's configuration features, specifically the data compression and remote system upgrade (RSU) and how they affect your design process.

For the supported features in each configuration scheme, refer to Table 2 on page 8.

## **Data Compression**

If you enable data compression, the Quartus II software generates configuration files with compressed configuration data. This compressed file reduces the storage requirements in the configuration device or flash memory and decreases the time needed to transmit the bitstream to the Cyclone III device. The time required by a Cyclone III device to decompress a configuration file is less than the time needed to transmit the configuration data to the device.

Cyclone III devices support decompression in the PS (when you use a MAX II device/microprocessor + flash) and AS configuration schemes. The Cyclone III decompression feature is not available in the AP, FPP, or JTAG configuration scheme.

To enable compression before compilation, enable Generate compressed bitstreams on the **Configuration** tab of the **Device & Pin Options** dialog box. You can also enable compression when creating programming files from the Convert **Programming Files** window. Open the **Properties** dialog box for the programming file, and turn on **Compression**.

For more information about data compression, refer to the Configuration, Design Security, and Remote System Upgrades in the Cyclone III Device Family chapter in the Cyclone III Device Handbook.

Early System Planning Page 11

### **Remote System Upgrade**

Cyclone III devices support remote update in the AS and AP configuration schemes. You can enable or disable remote update mode with an option setting in the Quartus II software. You can implement remote update in conjunction with real-time decompression of configuration data if you must save configuration memory space in the serial configuration device with AS configuration. To implement the remote system upgrade interface, you can use the altremote\_update megafunction.

For more information about the altremote\_update megafunction, refer to the *Remote System Upgrade* (ALTREMOTE\_UPDATE) Megafunction User Guide.

## **Phase-Locked Loop**

Cyclone III PLLs have a number of advanced features available including clock multiplication and division, phase shifting, programmable duty cycles, clock switchover, PLL cascading, PLL dynamic reconfiguration, dynamic phase shifting, spread-spectrum clocking, external clock outputs and control signals.

For more information about the PLL features, refer to the *Clock Networks and PLLs in Cyclone III Device Family* chapter in the *Cyclone III Device Handbook*.

Previously, PLLs in the Cyclone series devices' FPGAs were designed to be configured for a specific input frequency. The newly added voltage-controlled oscillator (VCO) range detector in the Cyclone III PLLs, together with the dynamic phase reconfiguration and PLL reconfiguration, enable the support for advanced display applications where the PLL input frequency may not be known ahead of time or may change.

For information about the VCO range detector and the reference design to support the unknown  $F_{ref}$  video applications, refer to Supporting Unknown  $F_{REF}$  Video Applications with PLLs white paper.

### **PLL Applications**

In general, you can use the PLLs for frequency synthesis and clock management. The PLL usage helps to compensate the clock delay for large clock networks to improve performance. You can also use the PLLs to recover clocks and clean jitter caused by the transmission signal line. The programmability of the FPGA makes it easy to change the parameters such as the frequency, bandwidth and duty cycle.

Before you start your design using a PLL, make sure you define the correct applications for the PLL.

Page 12 Early System Planning

### **Define PLL Settings**

Based on the features that are available in the Cyclone III device that you are targeting, define the settings of the PLL based on the system requirement. The following guidelines help you to decide on the settings.

### **PLL Input and Output Frequencies**

Based on your system requirement, define the input frequencies and output frequencies for the PLL. Cyclone III PLLs can operate in a particular bandwidth. If the input frequencies and output frequencies do not meet that bandwidth, you can cascade the PLLs. Cyclone III PLL clock inputs can only be fed by dedicated clock input pins or outputs from another PLL. PLL clock inputs cannot be fed by internally generated logic or clock source that originates from the general purpose I/O pins. PLL clock outputs can drive the dedicated clock output pin or global clock networks.

To find out whether the input frequencies and output frequencies can be implemented in one PLL, enter your settings when instantiating the altpll megafunction through the Quartus II software.

To obtain the input and output clock frequency range specifications for the different device speed grades, refer to the *Cyclone III Device Datasheet* chapter in the *Cyclone III Device Handbook*

#### **Number of Clock Inputs**

Cyclone III PLLs can have a maximum of two clock inputs, where only one clock input functions at a time. You need two clock inputs for your PLL for applications such as clock redundancy or dual clock domain. Clock redundancy application ensures there is a back-up input clock in case the current clock is not present. A dual clock application enables the PLL to change to another input clock frequency during operation. This feature is called clock switchover.

Cyclone III devices have automatic and manual clock switchover. Automatic switchover enables the PLL to change to another clock input after the current clock input becomes unavailable. Manual clock switchover enables the user to control the switch of the input clocks.

If you do not use the PLL for these applications, one clock input is sufficient.

You can enable the clock switchover feature from the altpll megafunction.

### **Number of Clock Outputs**

Cyclone III PLLs can have a maximum of five clock outputs (c0-c4). You can connect the c0 clock output to the dedicated external clock output pin (recommended as this minimizes the clock jitter), normal user I/O or dedicated global clock network. The c1, c2, c3, and c4 clock outputs can be connected to the user I/O pins or dedicated global clock networks.

#### Clock Input and Output I/O Standard

Dedicated clock input pins can support all I/O standards supported by the Cyclone III device, except **PPDS**, **RSDS**, and **mini-LVDS**. Dedicated external clock output pins can support all I/O standards supported by the Cyclone III device.

**Early System Planning** Page 13

For more information about the I/O standard support, refer to the I/O Features in the Cyclone III Device Family chapter in the Cyclone III Device Handbook.

### **PLL Design**

After defining the requirements, these are the items that you must consider while designing the PLL according to your application.

### **Selecting the Right Compensation Mode**

Table 3 shows the four compensation modes that Cyclone III devices support.

**Table 3. Compensation Modes**

| Modes                           | Description                                                                                                                                                              |  |  |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Source-synchronous<br>Mode      | Select this mode if you want to maintain the same phase relationship between the clock and data from the input pins to the I/O element (IOE) register driven by the PLL. |  |  |

| No Compensation<br>Mode         | Select this mode if you want a better jitter performance at the PLL output.                                                                                              |  |  |

| Normal Mode                     | Select this mode if you want the clock edge at an IOE or Logic Element (LE) register driven by the PLL to be phase-aligned with the clock signal at the clock input pin. |  |  |

| Zero Delay Buffer<br>(ZDB) Mode | Select this mode if you want the external clock output pin to be phase-aligned with the clock input pin for zero delay through the device.                               |  |  |

#### **PLL Dynamic Reconfiguration and Phase Stepping**

You can use this feature if you want to change the PLL settings without needing to reconfigure the entire device. Two main applications for this feature change between two output frequencies to suit the design and to adjust the clock-to-output (t<sub>CO</sub>) delays in real time without the need to regenerate a configuration file with new PLL settings.

You can enable the dynamic reconfiguration feature by instantiating the altpll megafunction. Then, you can ease the usage of this feature by instantiating the altpll\_reconfig megafunction.

To obtain the maximum reconfiguration clock frequency (fscanclk) and typical time required to reconfigure the scan chains (tconfigpl1), refer to the Cyclone III Device Datasheet in the Cyclone III Device Handbook.

Page 14 Early System Planning

#### **PLL Control Signals**

There are three main control signals, which are essential during PLL usage, depending on the application.

**Table 4. Compensation Modes**

| Signal | Description                                                                                                                                                                                                                                                                                                                                                      |  |  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| areset | When enabled, this control pin is an input reset pin for each PLL. You must enable this control pin if you enable the dynamic reconfiguration and clock switchover feature. You should also enable the automatic reset upon loss of lock feature using the altpll megafunction so that the PLL resets automatically when the locked signal goes low.             |  |  |

|        | Refer to the <i>Cyclone III Device Datasheet</i> in the <i>Cyclone III Device Handbook</i> to obtain the minimum pulse width on the areset signal (t <sub>ARESET</sub> ).                                                                                                                                                                                        |  |  |

| locked | When enabled, this control pin is an output pin for each PLL. When it is high, the PLL has locked onto the reference clock and the PLL clock outputs are operating at the desired phase and frequency. You should create a design to monitor this signal to ensure that the system using the PLL clock outputs reacts according to the validity of clock output. |  |  |

| pfdena | When enabled, this control pin is an input pin for each PLL. You should enable this pin if your system requires a certain clock frequency from the PLL even though the input clock is disabled, so that it will have time to store its current setting before shutting down.                                                                                     |  |  |

## **Planning for On-Chip Debugging**

The Quartus II software includes various debugging tools. The following is the list of debugging tools and their use as well as the requirement for using the tools. Using these tools in your design flow is optional, but is recommended.

## **SignalProbe Incremental Routing**

The SignalProbe Incremental Routing feature allows you to route internal signals to I/O pins without affecting the routing of the original design. Starting with a fully routed design, you can select and route the signals for debugging to either previously reserved or currently unused I/O pins. To use the SignalProbe feature, you must have additional I/Os in your device for the signals to be routed to. These I/Os should be routed out on the board in order for you to be able to probe the signals. You can use the SignalProbe feature to monitor synchronous or asynchronous signals.

For more information about ways to use the SignalProbe feature for debugging, refer to the *Quick Design Debugging Using SignalProbe* chapter in the *Quartus II Handbook*.

## SignalTap II Logic Analyzer

The SignalTap II Logic Analyzer captures and displays real-time behavior of your FPGA design's internal and I/O signals while the design is running at full speed, without the need for additional I/O pins or external probes.

You can use the SignalTap II Logic Analyzer by instantiating the SignalTap II Logic Analyzer megafunction and includes that in your design or by creating a SignalTap II Logic Analyzer (.stp) file so that you do not need to modify your design. The SignalTap II Logic Analyzer is suitable for capturing synchronous signals and needs a clock signal from your design to control data acquisition. The SignalTap II Logic Analyzer requires JTAG connection and communicates with the device through an Altera download cable. Additional LEs and the M9K memory are needed as well.

Early System Planning Page 15

To minimize changes to your Cyclone III device's performance and reduce compilation time when you use the SignalTap II Logic Analyzer, back-annotate your design and use incremental compilation.

For more information about how to use the SignalTap II Logic Analyzer for debugging, refer to the *Design Debugging Using the SignalTap II Logic Analyzer* chapter in the *Quartus II Handbook*.

### **Logic Analyzer Interface**

Logic Analyzer Interface enables you to connect and transmit the internal FPGA signals to an external logic analyzer or a mixed signal oscilloscope for analysis. You can use this feature to connect a large set of internal device signals to a small number of output pins for debugging purposes. This feature functions as a multiplexer and you can select which of the signal groups to be connected to the output pins for monitoring on the fly, without the need to recompile the design or reconfigure the FPGA.

The Logic Analyzer Interface requires JTAG connection and communicates with the device through an Altera download cable. Additional LEs and I/Os are needed as well.

For more information about ways to use the Logic Analyzer Interface feature for debugging, refer to the *In-System Debugging Using External Logic Analyzers* chapter in the *Quartus II Handbook*.

## **In-System Memory Content Editor**

The In-System Memory Content Editor feature allows you to modify the content of the memory or constant through the JTAG interface. This is useful in debugging for design examples that perform read and write operation on the memory so that you can check whether the design writes or reads the correct data to or from the memory. Changes to the memory or constant can be done without interrupting the device's functionality.

Specify that the memory or constant are modifiable when instantiating the megafunction for the memory or constant. The In-System Memory Content Editor requires JTAG connection and communicates with the device through an Altera download cable. Additional LEs are needed when this feature is turned on.

For more information on ways to use the In-System Memory Content Editor to access the on-chip memory, refer to the *In-System Updating of Memory and Constants* chapter in the *Quartus II Handbook*.

### **In-System Sources and Probes**

This feature allows you to input simple virtual stimuli and capture the current value of internal nodes in your design dynamically without the use of any external test equipment. You can force trigger conditions set up using the SignalTap II Logic Analyzer. The feature needs the altsource\_probe megafunction instantiated in your design before compilation and requires JTAG connection for the communication through an Altera download cable. Additional LEs are needed when this feature is used.

Page 16 **Board Design Considerations**

For more information on ways to use the In-System Source and Probes for debugging, refer to the Design Debugging Using In-System Sources and Probes chapter in the Quartus II Handbook.

### **Virtual JTAG Megafunction**

Similar to the in-System Sources and Probes, the Virtual JTAG megafunction allows you to apply virtual stimuli and capture the current value of internal nodes in your design dynamically without the use of any external test equipment, albeit the Virtual JTAG megafunction gives you a greater level of control but at the cost of greater complexity. The feature needs the sld\_virtual\_jtag megafunction instantiated in your design before compilation and requires JTAG connection for the communication through an Altera download cable. Additional LEs are needed when this feature is

For more information on ways to use the sld\_virtual\_jtag megafunction for debugging, refer to the Virtual JTAG (sld\_virtual\_jtag) Megafunction User Guide.

# **Board Design Considerations**

This section contains the information for your consideration when designing the board.

## I/O Consideration

### 3.3/3.0/2.5V LVTTL/LVCMOS Interface

Cyclone III devices are designed to support interface voltage levels from 1.2 V up to 3.3 V to accommodate the need for flexible I/O interface implementation. You can use Cyclone III devices to directly drive out 3.3-V LVTTL at up to 8 mA and 3.3-V LVCMOS at up to 2 mA. When using Cyclone III devices as a receiver in 3.3/3.0/2.5-V LVTTL/LVCMOS systems, you must follow the operating conditions including the Cyclone III absolute maximum DC input voltage and maximum allowed overshoot/undershoot voltage conditions.

- For the values of the absolute maximum DC input voltage and maximum allowed overshoot/undershoot voltage, refer to the Cyclone III Device Datasheet in the Cyclone III Device Handbook.

- Follow the guidelines in AN 447: Interfacing Cyclone III and Cyclone IV Devices with 3.3/3.0/2.5 V LVTTL/LVCMOS I/O Systems to ensure the device reliability when interfacing Cyclone III with 3.3/3.0/2.5 V voltage levels.

### **Pad Placement Consideration**

The V<sub>CCIO</sub> supply for a bank is susceptible to noise from switching outputs in the bank. To maintain an acceptable noise level on the V<sub>CCIO</sub> supply, there are restrictions on placement of single-ended I/O pads in relation to differential pads. The Quartus II software automatically checks for these restrictions.

Board Design Considerations Page 17

When single-ended voltage-referenced inputs are used in a bank, the Quartus II software automatically checks for restrictions about the placement of outputs in relation to  $V_{REF}$  pads and supply pairs ( $V_{CCIO}$  and GND). The restriction is in place to maintain acceptable noise level on the  $V_{CCIO}$  supply and prevent output switching noise from shifting the  $V_{REF}$  rail.

For placement guidelines for single-ended pads with respect to differential pads for each supported differential I/O standards, and for input, output and bidirectional pads when voltage referenced input pads exist in a bank, refer to the "Pad Placement and DC Guidelines" section in the I/O Features in the Cyclone III Device Family chapter

In specific applications, you can relax the restriction checks in the Quartus II software. For example, if you have a non-toggling single-ended pin, you can place it closer to a differential pin safely—bypassing the pin placement checks. To set this in the Quartus II software, assign 0 MHz toggle rate to Toggle Rate assignments for the pin in the Assignment Editor.

The Output Enable Group assignment is another useful setting especially in external memory interfaces to allow efficient placement of output or bidirectional pins in a  $V_{REF}$  group when a voltage referenced input is used in the group.

For details about implementing these features, refer to the *I/O Management* chapter in the *Quartus II Handbook*.

### **Minimizing Simultaneous Switching Noise**

of the Cyclone III Device Handbook.

Simultaneous switching noise (SSN) becomes a concern when too many pins within close proximity change levels at the same time and cause  $V_{CC}$  sag or ground bounce on the quiet pins nearby. Noise generated by SSN can reduce noise margin and cause incorrect switching.

When creating your design, try to separate the pins that switch simultaneously. If possible, distribute the switching pins to different I/O banks. Set the unused I/O pins nearby to  $V_{CC}$  to minimize  $V_{CC}$  sag, or to ground to minimize ground bounce. You can also turn on the slow slew rate feature and use a lower drive strength for the switching pins. Proper termination on the switching I/O pins also helps to reduce reflection and the SSN effect on the quiet pins.

- For details about the sources of the SSN, ways to mitigate SSN and guidelines on a PCB design for the general high speed digital designs, refer to *AN 508: Cyclone III Simultaneous Switching Noise (SSN) Design Guidelines*.

- For board design guidelines, refer to AN 224: High-Speed Board Layout Guidelines and AN 315: Guidelines for Designing High-Speed FPGA PCBs.

Page 18 Board Design Considerations

### **Unused Pin Connection**

The Quartus II software generates the pin report file (.pin) when you compile your design. This report file specifies how you should connect the unused pins of your device. For a Cyclone III device, depending on how you set the unused pins in the Quartus II software, unused I/O pins are marked in the report file as any one of the following items:

- GND\*

- RESERVED

- RESERVED\_INPUT

- RESERVED\_INPUT\_WITH\_WEAK\_PULLUP

- RESERVED\_INPUT\_WITH\_BUS\_HOLD

All I/O pins specified as GND\* can be connected to ground to improve the device's immunity to noise, or left unconnected. Leave all RESERVED I/O pins unconnected on your board because these I/O pins drive out unspecified signals. Tying a RESERVED I/O pin to  $V_{CC}$ , ground, or another signal source can create contention that can damage the output driver of the device.

RESERVED\_INPUT I/O pins can be connected to a high or low signal on the board while RESERVED\_INPUT\_WITH\_WEAK\_PULLUP and RESERVED\_INPUT\_WITH\_BUS\_HOLD pins can be left unconnected.

### **Termination Schemes**

Correct termination is important to prevent signal reflection on the signal lines. Depending on the I/O standards used and the direction of the signals travel, the termination scheme you should use on the boards may be different:

- You can use series and parallel termination.

- In general, series termination is normally used at the transmitter while parallel termination is used at the receiver.

- The value of the termination resistors should match the trace impedance.

- You can perform board-level simulation to obtain the suitable resistance values based on your termination scheme.

The Cyclone III device has on-chip series termination (with and without calibration) that you can use to replace the series termination resistors on your board.

For information about the various termination schemes, refer to the following documents:

- I/O Features in the Cyclone III Device Family chapter in the Cyclone III Device Handbook

- AN 224: High-Speed Board Layout Guidelines

- AN 315: Guidelines for Designing High-Speed FPGA PCBs

Board Design Considerations Page 19

#### **Board-Level Simulation**

To ensure that the selected I/O signaling meets receiver threshold levels with the board setup, perform simulation with third-party board-level simulation tools using the Cyclone III IBIS or HSPICE model.

Both the IBIS and HSPICE models describe the behavior of I/O buffers, but in a different way. The IBIS models describe the I/O buffers with voltage-current and voltage-time data curves while the HSPICE models describe the I/O buffers by their physical properties, such as transistor characteristics, parasitic capacitance and their connections to one another.

You can download the IBIS and HSPICE models from www.altera.com. You can also use the Quartus II software to create custom IBIS and HSPICE models for your design and perform simulation with the models to check the effect of the termination scheme on your board signals.

For information about performing simulation with IBIS and HSPICE models, refer to the *Signal Integrity Analysis with Third-Party Tools* chapter in the *Quartus II Handbook*.

## **Power Consideration**

Table 5 lists the external power supplies required to power Cyclone III devices.

Table 5. Cyclone III Power Supply Requirements

| Power Supply         | Description                                                           |  |

|----------------------|-----------------------------------------------------------------------|--|

| V <sub>CCINT</sub>   | Core voltage power supply                                             |  |

| V <sub>CCIO</sub>    | I/O power supply to the input and output buffers in Bank 1 to Bank 8. |  |

| V <sub>CCA</sub>     | Analog power supply for PLL.                                          |  |

| V <sub>CCD_PLL</sub> | Digital power supply for PLL.                                         |  |

| V <sub>REF</sub>     | Input reference voltage for voltage-reference I/O standards.          |  |

For the possible values of each power supply and the recommendation operation conditions, refer to the *Cyclone III Device Datasheet* chapter in the *Cyclone III Device Handbook*.

The  $V_{\rm CCIO}$  pin connections depend on the design's I/O standards, and support 1.2, 1.5, 1.8, 2.5, 3.0 and 3.3 V. Each bank can support a different voltage level. The  $V_{\rm REF}$  pin serves as an input reference voltage for the voltage reference I/O standards and is used mainly for a voltage bias and does not source or sink much current. The voltage can be created with a regulator or a resistor divider network. If voltage reference I/O standards are not used in the bank, the VREF pins are available as user I/O pins

Altera suggests that you use a linear regulator to power the  $V_{CCA}$  pins because they power the analog circuitry. You can power the digital voltage rails with the linear or switching regulators depending on the efficiency or cost considerations.

To reduce system noise, it is important to ensure that the power supply is clean. Place a ferrite bead and tantalum parallel capacitors where the power supply enters the board's power plane to filter out the noise to the power plane. Generally, the tantalum capacitors are used for circuits which demand high stability in the capacitance values.

Page 20 Board Design Considerations

The ferrite bead should be connected in series between the power supply and the power plane, while the capacitors are connected between the power plane and ground, in parallel with each other. Decoupling depends on the design decoupling requirements of the specific board.

For information on minimizing noise for power supplies, refer to the following documents:

- AN 224: High-Speed Board Layout Guidelines

- *AN 315: Guidelines for Designing High-Speed FPGA PCBs.*

The PLL contains analog components embedded in a digital device. Consider the following items for designing the PLL power supply and minimizing jitter:

- Run a thick trace (at least 20 mils) from the power supply to each VCCA pin.

- Connect all VCCD\_Pll power pins to the quietest digital supply on the board.

- Ensure that all VCCA and VCCD\_PLL power pins are connected to a 2.5-V and 1.2-V power supply respectively, even if you are not using any PLL in the device.

- Use an isolated linear regulator to power the VCCA pin.

- Connect the VCCD\_PLL power pin to the quietest digital supply on the board.

- Filter each VCCA and VCCD\_PLL power pin with a decoupling circuit. Refer to the Cyclone III device pin-out for recommendation.

- Connect the GNDA pins to an isolated analog ground plane on the board.

- For more information about the decoupling strategy for Cyclone III power supplies, refer to Cyclone III Device Family Pin Connection Guidelines.

## **Device Power-up**

In many applications, knowing the power-up behavior of your device is critical, especially when you are inserting or removing the board in a system during system operation. Among the considerations are I/O behaviors, and the conditions of supplies and timing.

Review the conditions and considerations discussed in this section before you begin with board design and configuration setup to ensure a successful implementation of Cyclone III devices in your design.

### **Technology**

Cyclone III devices feature hot-socketing and power-on reset (POR) circuitry that regulates the power-up sequencing of the device before configuration:

- The circuitries ensure that the Cyclone III devices are ready for configuration while taking care of uncertainties on device interfaces during these stages

- The circuitries enable the Cyclone III device to be hot-swapped without the use of any external devices.

Board Design Considerations Page 21

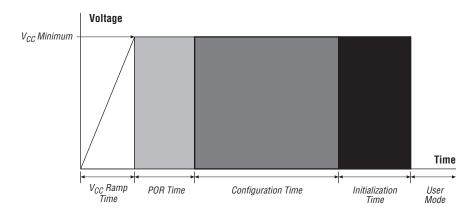

Figure 1 shows the power-up stages of a Cyclone III device.

Figure 1. Cyclone III Power-Up Stages

### Note to Figure 1:

(1)  $V_{CC}$  ramp must be monotonic.

For more details about hot socketing and power-on reset circuit operation, refer to the *Hot Socketing and Power-On Reset in the Cyclone III Device Family* chapter in the *Cyclone III Device Handbook*.

Page 22 Board Design Considerations

## **Requirements and Behavior**

The requirement and behavior of a Cyclone III device are listed in Table 6 for each stage before configuration.

Table 6. Requirement and Behavior of Device During Various Power-up Stages

| Ctowns               | Setup                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                            |  |  |  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Stages               | Requirement                                                                                                                                                                                                                                                                                    | Behavior                                                                                                                                                                                   |  |  |  |

| Pre-Power Up         | Signals can be driven into Cyclone III I/O pins,<br>dedicated inputs and dedicated clock pins<br>without damaging the device.                                                                                                                                                                  |                                                                                                                                                                                            |  |  |  |

|                      | ■ Determine the required POR time for your device; fast POR (3 ms to 9 ms) or standard POR (50 ms to 200 ms). Selection is determined by MSEL pins setting.                                                                                                                                    | Not applicable                                                                                                                                                                             |  |  |  |

|                      | Can support any power-up sequence of supplies.                                                                                                                                                                                                                                                 | Output buffers tri-stated for all conditions, for                                                                                                                                          |  |  |  |

| V <sub>CC</sub> Ramp | V <sub>CCIO</sub> , V <sub>CCINT</sub> , and V <sub>CCA</sub> are required. V <sub>CCIO</sub> for banks with configuration pins (1, 6, 7, and 8) are required.                                                                                                                                 | <ul> <li>example:</li> <li>when V<sub>CCIO</sub> is powered before V<sub>CCINT</sub></li> <li>if the I/O pad voltage is higher than V<sub>CCIO</sub></li> </ul>                            |  |  |  |

|                      | Supplies must meet ramp rate according to<br>required POR; 50 μs to 3 ms for fast POR or<br>50 ms for standard POR. Fast POR is used when<br>Cyclone III device is required to wake up quickly<br>to begin operation. Select POR using MSEL pin<br>settings—refer to the Configuration, Design | <ul> <li>sudden voltage spikes (overshoot) during<br/>hot-socketing.</li> </ul>                                                                                                            |  |  |  |

|                      |                                                                                                                                                                                                                                                                                                | <ul> <li>Exception for configuration pins, which are<br/>expected to drive out during power-up cycle. No<br/>hot socketing circuit for these pins.</li> </ul>                              |  |  |  |

|                      | Security, and Remote System Upgrades in the Cyclone III Device Family chapter in the Cyclone III Device Handbook.                                                                                                                                                                              | No current path exists from I/O pin to V <sub>CCINT</sub> or V <sub>CCIO</sub> , as hot-socketing circuit is enabled. Refer to the Hot Socketing and Power-On Reset in the                 |  |  |  |

|                      | V <sub>CC</sub> ramp must be monotonic.                                                                                                                                                                                                                                                        | Cyclone II Device Family chapter in the Cyclone III Device Handbook for leakage or driving current during hot-socketing.                                                                   |  |  |  |

|                      |                                                                                                                                                                                                                                                                                                | Safe from latch-up, no low-impedance path from<br>V <sub>CC</sub> to GND that may result in large current<br>passing through the path.                                                     |  |  |  |

|                      | Maintain V <sub>CC</sub> ramp to desired operating voltage                                                                                                                                                                                                                                     | Output buffers remain tri-stated.                                                                                                                                                          |  |  |  |

| POR                  | <ul> <li>level.</li> <li>If maximum V<sub>CC</sub> ramp time cannot be met, use an external component to hold nconfig low until the power supplies have reached their minimum recommended operating levels. Else, the device may not configure properly and enter user mode.</li> </ul>        | <ul> <li>POR circuit keeps device in reset state until all<br/>V<sub>CC</sub> supplies have stabilized and reached<br/>acceptable levels before configuration is<br/>triggered.</li> </ul> |  |  |  |

After the Cyclone III device enters user mode, the POR circuit continues to monitor the VCCINT and VCCA pins so that a brown-out condition during user mode can be detected. If the  $V_{CCINT}$  and  $V_{CCA}$  voltage sags below the POR trip point during user mode, the POR circuit resets the device. The POR circuit does not reset the device if the  $V_{CCIO}$  voltage sags during user mode.

For more information about power-on reset, refer to the *Hot Socketing and Power-On Reset in Cyclone III Device Family* chapter in the *Cyclone III Device Handbook*.

**Board Design Considerations** Page 23

# **Configuration Pin Connections**

Depending on your configuration scheme, different pull-up or pull-down resistor or signal integrity requirements may apply. Some configuration pins also have specific requirements if unused. It is important to correctly connect the configuration pins. This section provides guidelines to address common issues.

The internal PCI clamping diode for the dual-purpose configuration pin is turned off if the pin is part of the selected configuration scheme in your Quartus II project.

For a list of the dedicated and dual-purpose configuration pins, and a description of the function and connection guidelines, refer to the Configuration, Design Security, and Remote System Upgrades in the Cyclone III Device Family chapter in the Cyclone III Device Handbook.

### **Configuration and JTAG Pins I/O Voltage Requirements**

When using a serial configuration device in the AS configuration scheme, you must connect a 25- $\Omega$  series resistor at the near end of the serial configuration device for the DATA [0]. When cascading Cyclone III devices in multi-device configuration, you must connect repeater buffers between the Cyclone III master and slave device for DATA and DCLK. The output resistance of the repeater buffers has to fit the maximum overshoot equation given by  $0.8Z_O = R_E = 1.8Z_O$ . In this equation,  $Z_O$  is the transmission line impedance and R<sub>E</sub> is the equivalent resistance of the output buffer.

For information about configuration requirements, refer to the Configuration, Design Security, and Remote System Upgrades in the Cyclone III Device Family chapter in the Cyclone III Device Handbook.

## DCLK/TCK Signal Integrity

Adopt good design techniques to ensure that the DCLK and TCK traces on your board produce clean signals with no overshoot, undershoot, or ringing. When designing the board, lay out the DCLK and TCK traces using the same techniques used to lay out a clock line. A noisy DCLK signal could affect configuration and cause an nSTATUS error. Ensure that the TCK trace produces a clean signal with no overshoot, undershoot, or ringing. For a chain of Cyclone III devices, noise on any of the DCLK or TCK pins of each device in the chain could cause configuration or JTAG programming to fail for the whole chain.

For more information about connecting devices in a chain, refer to the Configuration, Design Security, and Remote System Upgrades in the Cyclone III Device Family chapter in the Cyclone III Device Handbook.

### JTAG/Configuration Pin Pull-up/Down

Noise at the JTAG pins, whether the device is in ISP or user mode, or during power up, can cause the device to go into an undefined state or mode. Altera recommends pulling the TCK pin low and the TMS pin high through resistors.

Page 24 Board Design Considerations

The JTAG circuitry is activated when  $V_{CCINT}$  is powered up. If the TMS and TCK pins are connected to  $V_{CCIO}$  and the  $V_{CCIO}$  is not powered up, the JTAG signals are left floating. Any transition on the TCK pin can cause the JTAG state machine to transition to an unknown state, leading to incorrect operation when  $V_{CCIO}$  is finally powered up. To disable the JTAG state machine during power-up, the TCK pin should be pulled low to ensure that an inadvertent rising edge does not occur on TCK.

### **JTAG/Configuration Chain Connection**

Connect the JTAG pins of the device to the download cable header correctly. If you have more than one device in the chain, connect the TDO pin of a device to the TDI pin of the next device in the chain.

All I/O inputs must maintain a maximum AC voltage of 4.1 V. Because JTAG pins do not have the internal PCI clamping diodes to prevent voltage overshoot when using V<sub>CCIO</sub> of 2.5 V, 3.0 V or 3.3 V, you must power up the download cable's V<sub>CC</sub> with a 2.5 V supply from V<sub>CCA</sub>. When using device V<sub>CCIO</sub> of 1.2 V, 1.5 V, or 1.8 V, you can power up the download cable's V<sub>CC</sub> with the supply from V<sub>CCIO</sub>.

For more information on JTAG configuration chain, refer to the *Configuration*, *Design Security*, and *Remote System Upgrades* in the Cyclone III Device Family chapter in the *Cyclone III Device Handbook*. You can also cascade the FPGA devices in chain in other configuration schemes such as AS, AP, PS, and FPP.

### Multi Device Multi VCCIO (Level Shifter)

The operating voltage supplied to the Altera download cable by the target board through the 10-pin header determines the I/O voltage level of the download cable. The JTAG pins for all Cyclone III devices reside in Bank 1 and their I/O standard support is controlled by the  $V_{\text{CCIO}}$  setting for Bank 1.

As the download cable interfaces with the JTAG pins of your device, ensure that the download cable I/O voltage and the JTAG pin voltage are compatible. Table 7 shows the I/O voltages supported by different download cables.

| Download Cable               | I/O Voltage                           |                                        |                             |  |

|------------------------------|---------------------------------------|----------------------------------------|-----------------------------|--|

| Download Cable               | 2.5 V V <sub>CCA</sub> <sup>(1)</sup> | 1.8 V V <sub>CCIO</sub> <sup>(2)</sup> | 1.5 V V <sub>CCIO</sub> (2) |  |

| USB-Blaster <sup>TM</sup>    | ✓                                     | ✓                                      | _                           |  |

| ByteBlaster <sup>TM</sup> II | ✓                                     | ✓                                      | ~                           |  |

| ByteBlasterMV <sup>TM</sup>  | ✓                                     | _                                      | _                           |  |

| MasterBlaster <sup>TM</sup>  | ✓                                     | _                                      | _                           |  |

Table 7. Download Cable I/O Voltage

#### Notes to Table 7:

- (1) When interfacing the download cables with the Cyclone III device, you must ensure that all I/O inputs to the device maintain a maximum AC voltage of 4.1 V. Altera recommends powering up the download cables with V<sub>CCA</sub> of 2.5 V when using V<sub>CCIO</sub> of 2.5 V, 3.0 V, or 3.3 V on your Cyclone III devices.

- (2) When using device  $V_{CCIO}$  of 1.2 V, 1.5 V, or 1.8 V, you can power up the download cable's  $V_{CC}$  with the supply from  $V_{CCIO}$ . However, Altera download cables do not support a target supply voltage of 1.2 V.

Board Design Considerations Page 25

For more information about JTAG configuration with Altera download cables, refer to the *Configuration, Design Security, and Remote System Upgrades* in the Cyclone III Device Family chapter in the *Cyclone III Device Handbook,* and the appropriate download cable user guide.

In a JTAG chain containing devices with different  $V_{CCIO}$ , the devices with a higher  $V_{CCIO}$  level should drive the devices with the same or lower  $V_{CCIO}$  level. All I/O inputs must maintain a maximum AC voltage of 4.1 V. To prevent voltage overshoot when using  $V_{CCIO}$  of 2.5 V, 3.0 V, or 3.3 V, you must power up the download cable's  $V_{CC}$  with a 2.5 V supply from  $V_{CCA}$ . When using device  $V_{CCIO}$  of 1.2 V, 1.5 V, or 1.8 V, you can power up the download cable's  $V_{CC}$  with the supply from  $V_{CCIO}$ . However, Altera download cables do not support a target supply voltage of 1.2 V. You only need one level shifter at the end of the chain with this device arrangement. If this arrangement is not possible, you have to add more level shifters into the chain. Figure 2 shows the JTAG chain that contains devices with different  $V_{CCIO}$ .

Power TDI from Must never exceed 2.5 V VCCA overshoot of 4.1 V TDI 3.3 V 3.0 V 2.5 V **VCCIO VCCIO** VCCIO Download cable header 1.5 V 1.8 V Level TDO VCCIO Shifter VCCIO Shift TDO to level acceptable by tester if necessary

Figure 2. Devices with Different VCCIO in a JTAG Chain

### **JTAG Signal Buffering**

The JTAG signal integrity determines the need to buffer a JTAG chain. Pay particular attention to the TCK signal because it is the JTAG clock and is the fastest switching signal compared to the other JTAG signals. Altera recommends buffering the signals at the connector because cables and board connectors tend to act as poor transmission lines and introduce noise to the signals. After this initial buffer at the connector, add buffers as the chain gets longer or whenever the signals must cross a board connector.

At any given time, when a cable must drive three or more devices, buffer the signal at the cable connector to prevent signal deterioration. The decision to buffer the signal also depends on the board layout, loads, connectors, jumpers, and switches on the board. Anything added to the board that affects the inductance or capacitance of the JTAG signals increases the likelihood of a buffer being added to the chain.

For the TCK and TMS signals that drive in parallel, each buffer should drive no greater than eight loads. If jumper or switches are added to the path, decrease the number of loads.

**Board Design Considerations** Page 26

## **Unused JTAG Pins Connection**

If you are not using the JTAG interface, make sure the JTAG pins on the Cyclone III device are not left floating and are connected to a stable level. Because JTAG configuration takes precedence over all other configuration methods, these pins should not be left floating or toggling during configuration.

### **MSEL Configuration Mode Pins**

Select the configuration scheme by driving the Cyclone III device MSEL pins either high or low. The MSEL pins are powered by the V<sub>CCINT</sub> power supply of the bank in which they reside. The MSEL [3..0] pins have  $5-k\Omega$  internal pull-down resistors that are always active. During power-on reset (POR) and during reconfiguration, the MSEL pins have to be at least LVTTL V<sub>IL</sub> or V<sub>IH</sub> levels to be considered a logic low or logic high, respectively. To avoid any problems with detecting an incorrect configuration scheme, hard wire the MSEL pins to  $V_{CCA}$  and GND without any pull-up or pull-down resistors. Alternatively, set up your board so that you can connect each pin to either  $V_{CCA}$  or GND with a 0- $\Omega$  resistor to change between configuration modes during testing or debugging. Altera recommends not to drive the MSEL pins with a microprocessor or another device.

Do not leave the MSEL pins floating.

For more information about configuration, refer to the Configuration, Design Security, and Remote System Upgrades in the Cyclone III Device Family chapter in the Cyclone III Device Handbook. Also refer to the Configuration Center, which includes links to troubleshooters that you can use to help debug configuration problems. To help you debug JTAG programming issues, refer to the JTAG Configuration & ISP Troubleshooter. To debug FPGA configuration issues, refer to the FPGA Configuration Troubleshooter.

#### **Configuration Devices**

The EPCS devices (EPCS4, EPCS16, EPCS64, and EPCS128) are used in the AS configuration scheme for Cyclone III devices.

For information about the EPCS devices, refer to the Serial Configuration (EPCS) Devices Datasheet.

#### **EPCS Connection**