# LTC3815

**NOLOGY** 6A Monolithic Synchronous DC/DC Step-Down Converter with Digital Power System Management **DESCRIPTION**

opment system.

### FEATURES

- 2.25V to 5.5V Input Voltage Range

- ±1% Total Output Voltage Accuracy Over Temperature at V<sub>IN</sub> = 3.3V or 5V

- Single Resistor-Programmable Output Voltage

- PMBus Compliant Serial Interface:

- Programmable Output Voltage Margining: Up to ±25% V<sub>OUT</sub> Range with 0.1% Resolution

- Read back of Average and Peak Temperature, Current, and Voltage (25Hz Refresh Rate)

- Fault Status

- Phase-Lockable Fixed Frequency Up to 3MHz

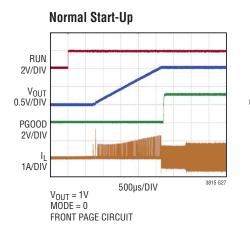

- Less Than 1ms Power-Up Time

- Integrated 13-Bit ADC

- Optional External Reference Input

- Pin Selectable Fast-Margining of the Output Voltage

- Power Good Flag with Pin Programmable Thresholds and Filter Delay

- Differential Remote Output Voltage Sensing

- Master Shutdown Mode: <1µA Supply Current</p>

- Clock Out for 2-Phase Operation (12A Output Current)

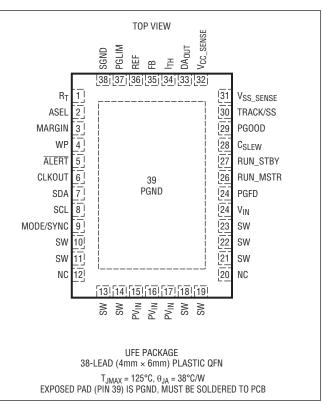

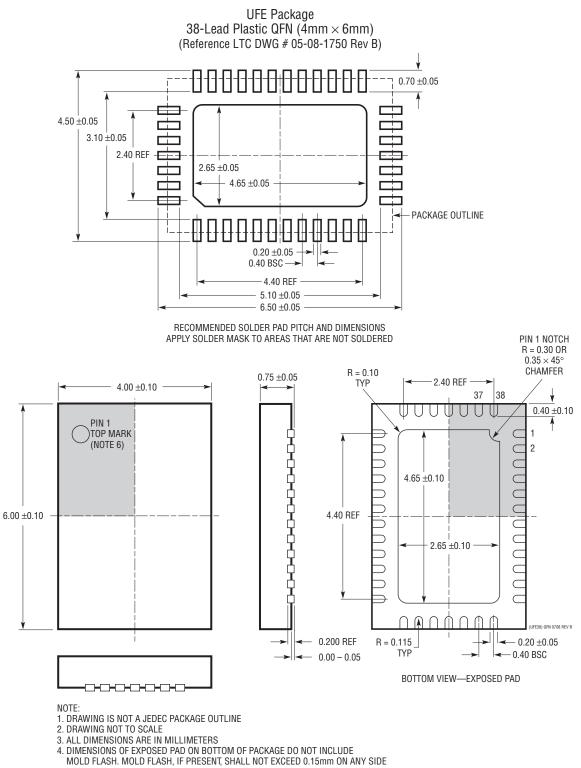

- Available in a Thermally-Enhanced 38-Lead 4mm × 6mm QFN Package

### **APPLICATIONS**

- Intelligent Energy Efficient Power Conversion

- ASIC/FPGA/Processor Power

- Distributed Power Systems

- Point of Load Power Conversion

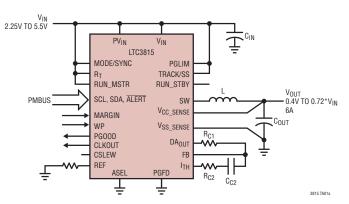

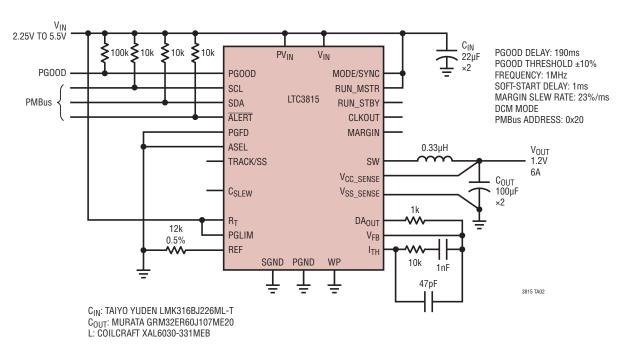

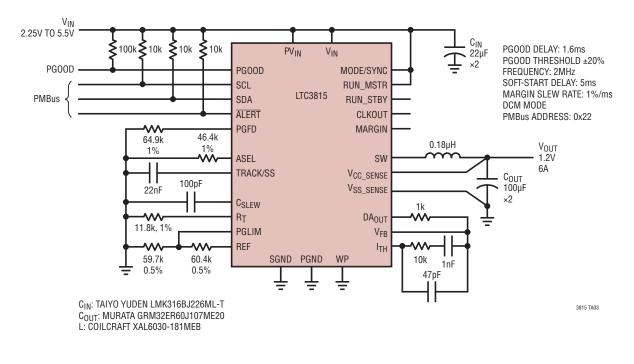

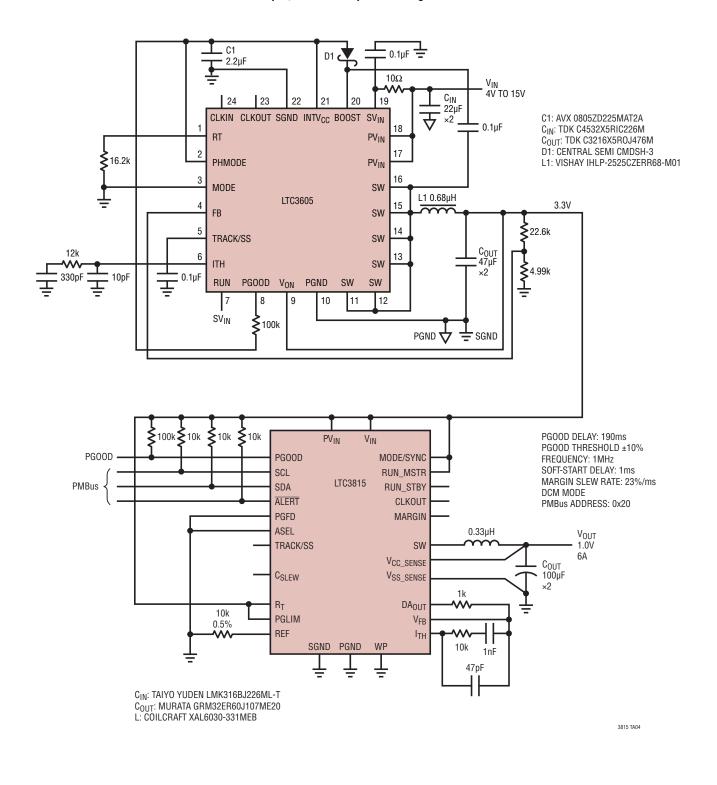

## TYPICAL APPLICATION

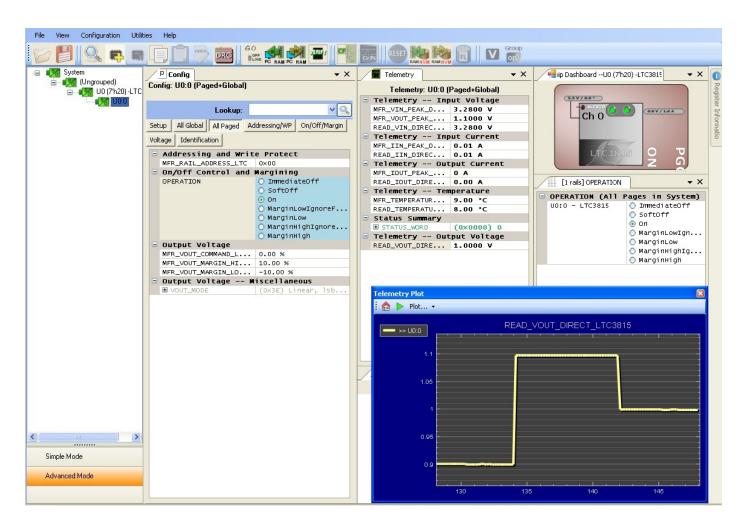

The LTC<sup>®</sup>3815 is a high efficiency, 6A monolithic synchronous buck regulator using a phase lockable controlled on-time, current mode architecture. The output voltage is programmable from 0.4V to 72% of V<sub>IN</sub> with a single external resistor or an external voltage reference through the reference input (REF) pin. The output voltage can be margined up or down up to  $\pm 25\%$  with 0.1% resolution via a PMBus-compliant serial interface. The serial interface can also be used to read back fault status and both timeaveraged (~4ms) and peak input/output current, input/ output voltage and temperature. System configuration

The architecture provides extremely fast transient response and allows operation at the very low on-times required to regulate low output voltages at high switching frequencies. The operating frequency is programmable from 400kHz to 3MHz with an external resistor or for noise sensitive applications, it can be synchronized to an external clock over the same range. The operating supply voltage range is from 2.25V to 5.5V making it suitable for operation from 2.5V, 3.3V or 5V rails or Lithium-Ion batteries.

and monitoring is supported by the LTpowerPlay<sup>®</sup> devel-

∠7, LT, LTC, LTM, Linear Technology, the Linear logo and LTpowerPlay are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners. Protected by U.S. Patents including 5481178, 5705919, 5929620, 6144194, 6177787, 6580258, 5408150, 7420359. Licensed under U.S. Patent 7000125 and other related patents worldwide.

# **ABSOLUTE MAXIMUM RATINGS**

(Notes 1, 7)

| $\label{eq:VIN} \begin{array}{l} V_{IN}, P_{VIN}0.3V \ to \ 6V \\ V_{CC\_SENSE}, V_{SS\_SENSE}, C_{SLEW}, R_T, I_{TH}, MODE/SYNC, \\ REF, TRACK/SS, PGFD, PGLIM, ASEL, DA_{OUT}, MARGIN, \\ RUN\_STBY, FB0.3V \ to \ (V_{IN} + 0.3V) \\ RUN\_MSTR, PGOOD, \overline{ALERT}, SCL, \end{array}$ |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SDA Voltage0.3V to 6V<br>WP0.3V to 2.5V<br>Operating Junction Temperature Range<br>(Notes 2, 3)40°C to 125°C<br>Storage Temperature Range65°C to 125°C                                                                                                                                        |  |

# PIN CONFIGURATION

# ORDER INFORMATION

(http://www.linear.com/product/LTC3815#orderinfo)

| LEAD FREE FINISH | TAPE AND REEL     | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|------------------|-------------------|---------------|---------------------------------|-------------------|

| LTC3815EUFE#PBF  | LTC3815EUFE#TRPBF | 3815          | 38-Lead (4mm × 6mm) Plastic QFN | -40°C to 125°C    |

| LTC3815IUFE#PBF  | LTC3815IUFE#TRPBF | 3815          | 38-Lead (4mm × 6mm) Plastic QFN | -40°C to 125°C    |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the specified operating junction temperature range, $V_{IN} = 3.3V$ unless otherwise noted. (Note 2)

| SYMBOL                                           | PARAMETER                                                                                             | CONDITIONS                                                                                                                                                                                         |   | MIN          | ТҮР               | MAX                    | UNITS                |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------|-------------------|------------------------|----------------------|

| V <sub>IN</sub>                                  | Input Supply Range                                                                                    |                                                                                                                                                                                                    | • | 2.25         |                   | 5.5                    | V                    |

| V <sub>OUT</sub>                                 | Output Voltage Programming Range                                                                      |                                                                                                                                                                                                    | • | 0.4          |                   | 72% of V <sub>IN</sub> | V                    |

| Ι <sub>Q</sub>                                   | V <sub>IN</sub> Supply Current<br>Normal Mode<br>Standby<br>Shutdown                                  | $\label{eq:VRUN_MSTR} \begin{array}{l} V_{RUN_MSTR} > 1V \mbox{ (Note 4)} \\ V_{RUN_STBY} = 0V, \mbox{ V}_{RUN_MSIR} > 1V \\ V_{RUN_MSTR} = 0V, \mbox{ V}_{SDA} = V_{SCL} \geq V_{IN} \end{array}$ |   |              | 5<br>120<br>1     | 8<br>200               | mA<br>μA<br>μA       |

| V <sub>UVLO</sub>                                | V <sub>IN</sub> Undervoltage Reset<br>Hysterisis                                                      | V <sub>IN</sub> Rising<br>V <sub>IN</sub> Falling                                                                                                                                                  |   | 2.05         | 2.15<br>0.2       | 2.25                   | V<br>V               |

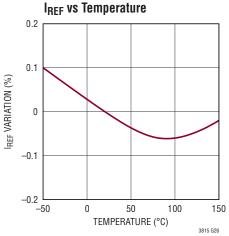

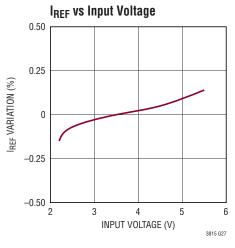

| I <sub>REF</sub>                                 | Reference Current                                                                                     | (Note 10)                                                                                                                                                                                          | • | 99.2<br>99.5 | 100<br>100        | 100.8<br>100.5         | μA<br>μA             |

| $\Delta I_{\text{REF,LINE}}$                     | Reference Current Line Regulation                                                                     | V <sub>IN</sub> = 2.5V to 5.5V (Note 10)                                                                                                                                                           |   |              | 0.05              | 0.2                    | %/V                  |

| ΔV <sub>OUT,OFFSET</sub>                         | Regulation Accuracy<br>$\Delta V_{OUT,OFFSET} = (V_{CC_SEN} - V_{SS_SEN}) - V_{REF}$                  | V <sub>REF</sub> = 1.5V (Notes 5, 10)                                                                                                                                                              | • | -0.5         |                   | 0.5                    | %                    |

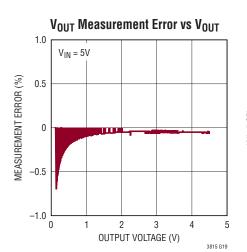

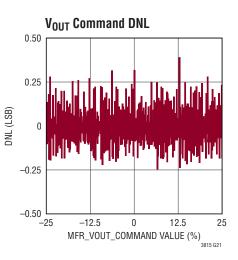

| $\Delta V_{OUT,MARGIN}$                          | Maximum Margining Range<br>Set Point Accuracy                                                         | MFR_VOUT_COMMAND = $-25\%$ to 25%, V <sub>REF</sub> = 1.5V (Note 5)                                                                                                                                | • | -25<br>-0.5  | 0                 | 25<br>0.5              | %<br>%               |

|                                                  | Resolution<br>LSD Step Size                                                                           |                                                                                                                                                                                                    |   |              | 9<br>0.1          |                        | Bits<br>%            |

| NL_V <sub>OUT</sub>                              | DAC Nonlinearity                                                                                      |                                                                                                                                                                                                    |   |              | -                 | ±1                     | LSB                  |

| A <sub>EA</sub>                                  | Error Amplifier Open Loop Gain                                                                        | I <sub>TH</sub> = 1V (Note 5)                                                                                                                                                                      |   |              | 80                |                        | dB                   |

| f <sub>BW</sub>                                  | Error Amp Gain Bandwidth Product                                                                      | (Note 6)                                                                                                                                                                                           |   |              | 20                |                        | MHz                  |

| R <sub>IN</sub>                                  | Differential Amplier Input Resistance                                                                 | Measured at V <sub>CC SEN</sub> Pin                                                                                                                                                                |   |              | 160               |                        | kΩ                   |

| t <sub>SS</sub>                                  | Internal Soft-Start Time/V <sub>BEF</sub>                                                             | External $C_{SS} = Float$                                                                                                                                                                          |   |              | 1                 |                        | ms/V                 |

| I <sub>CSLEW</sub>                               | C <sub>SLEW</sub> Pull-Up Current                                                                     | V <sub>CSLEW</sub> = 0V                                                                                                                                                                            |   |              | -10               |                        | μA                   |

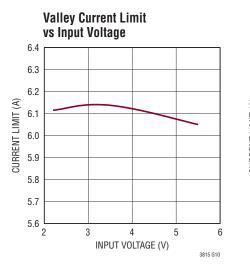

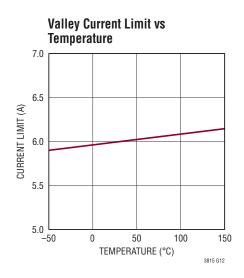

| ILIM                                             | SW Valley Current Limit                                                                               | Sourcing (Note 8)<br>Sinking                                                                                                                                                                       | • | 5.5          | 6.5<br><i>—</i> 6 | 7.5                    | A<br>A               |

| I <sub>RUN_STBY</sub>                            | Regulator On Source Current                                                                           | V <sub>RUN STBY</sub> = 0V                                                                                                                                                                         |   |              | -2.5              |                        | μA                   |

| V <sub>RUN_MSTR</sub>                            | Regulator On Threshold (Master Shutdown)<br>Regulator On Hysterisis<br>Regulator Power-Down Threshold | Rising Edge<br>Falling Edge<br>I <sub>O</sub> < 10µA                                                                                                                                               |   | 0.9          | 1<br>0.1<br>0.65  | 1.1                    | V<br>V<br>V          |

| V <sub>RUN_STBY</sub>                            | Regulator On Threshold (Standby Mode)                                                                 |                                                                                                                                                                                                    |   | 0.7          | 1                 | 1.2                    | V                    |

| I <sub>ASEL</sub>                                | ASEL Programming Current                                                                              |                                                                                                                                                                                                    |   |              | 10                |                        | μA                   |

| IPGFD                                            | PGFD Programming Current                                                                              |                                                                                                                                                                                                    |   |              | 10                |                        | μA                   |

| I <sub>SS</sub>                                  | SS Current                                                                                            | $V_{SS} = 0V$                                                                                                                                                                                      |   | 4            | 5                 | 6                      | μΑ                   |

| V <sub>IH,MARGIN</sub><br>V <sub>IL,MARGIN</sub> | MARGIN High Voltage<br>MARGIN Low Voltage                                                             |                                                                                                                                                                                                    |   | 1.2          |                   | 0.4                    | V                    |

| I <sub>WP</sub>                                  | WP Pin Pull-Up Current                                                                                | WP = 0V                                                                                                                                                                                            |   |              | 10                |                        | μA                   |

| SR <sub>MARGIN</sub>                             | Reference Slew Rate During Margin Change                                                              | C <sub>SLEW</sub> = 1nF<br>C <sub>SLEW</sub> = OPEN<br>C <sub>SLEW</sub> = SV <sub>IN</sub>                                                                                                        |   |              | 0.1<br>23<br>10   |                        | %/ms<br>%/ms<br>%/µs |

| t <sub>INIT</sub>                                | Initialization Time                                                                                   | Delay from Power Applied Until<br>V <sub>OUT</sub> Ramp Up                                                                                                                                         |   |              | 1                 | 2                      | ms                   |

| Oscillator and F                                 | Power Switch                                                                                          |                                                                                                                                                                                                    |   |              |                   | 1                      |                      |

| f <sub>OSC</sub>                                 | Oscillator Frequency                                                                                  | $R_T = 25.5k$<br>$R_T = SV_{IN}$                                                                                                                                                                   | • | 0.85<br>0.85 | 1.0<br>1.0        | 1.15<br>1.15           | MHz<br>MHz           |

| V <sub>SYNC</sub>                                | SYNC Level High<br>SYNC Level Low                                                                     |                                                                                                                                                                                                    |   | 1.2          |                   | 0.3                    | V<br>V               |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the specified operating junction temperature range, $V_{IN} = 3.3V$ unless otherwise noted. (Note 2)

| SYMBOL                       | PARAMETER                       | CONDITIONS                                                                                                              | MIN              | ТҮР              | MAX                | UNITS          |

|------------------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------|------------------|--------------------|----------------|

| V <sub>MODE</sub>            | Discontinuous Mode Threshold    |                                                                                                                         |                  | 1                |                    | V              |

| t <sub>ON(MIN)</sub>         | Minimum On-Time                 |                                                                                                                         |                  | 75               |                    | ns             |

| t <sub>OFF(MIN)</sub>        | Minimum Off-Time                |                                                                                                                         |                  | 100              |                    | ns             |

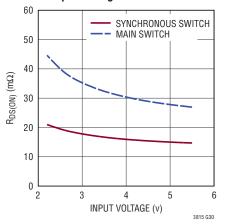

| R <sub>TOP</sub>             | Top Power PMOS On Resistance    |                                                                                                                         |                  | 35               |                    | mΩ             |

| R <sub>BOTTOM</sub>          | Bottom Power NMOS On Resistance |                                                                                                                         |                  | 20               |                    | mΩ             |

| θςικουτ                      | Relative Phase of CLKOUT        | MODE/SYNC = 0V                                                                                                          |                  | 180              |                    | Deg            |

| PGOOD                        |                                 |                                                                                                                         |                  |                  |                    | <u> </u>       |

| V <sub>PGOOD,DEFAULT</sub>   | Default PGOOD Threshold         | V <sub>PGLIM</sub> = V <sub>IN</sub> , V <sub>OUT</sub> >1V                                                             | ±8               | ±10              | ±12                | %              |

| V <sub>PG00D</sub> , PROGRAM | Program PGOOD Threshold         | $\label{eq:VPGLIM} \begin{array}{l} V_{PGLIM}/V_{REF} = 0.19,  V_{OUT} \geq 1V \\ V_{PGLIM}/V_{REF} = 0.38 \end{array}$ | ±6<br>±13        | ±10<br>±30       | ±9<br>±17          | %              |

| I <sub>LEAK</sub>            | PGOOD Leakage Current           |                                                                                                                         |                  |                  | ±5                 | μA             |

| V <sub>OL</sub>              | PGOOD Output Low Voltage        | I <sub>OUT</sub> = 3mA                                                                                                  |                  | 0.1              | 0.3                | V              |

| t <sub>PGFD</sub>            | PGOOD Filter Delay              | PGFD = 0V<br>PGFD = 0.65V<br>PGFD = V <sub>IN</sub>                                                                     | 150<br>1.0<br>17 | 190<br>1.6<br>24 | 250<br>2.2<br>32.5 | μs<br>ms<br>ms |

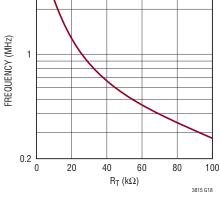

| Output Voltage R             | eadback                         |                                                                                                                         |                  |                  |                    | <u> </u>       |

| N                            | Resolution<br>LSB Step Size     |                                                                                                                         |                  | 13<br>0.5        |                    | Bits<br>mV     |

| V <sub>F/S</sub>             | Full Scale Output Voltage       | (Note 9)                                                                                                                |                  | 16.4             |                    | V              |

| V <sub>OUT_TUE</sub>         | Total Unadjusted Error          |                                                                                                                         | •                |                  | ±0.75<br>±0.5      | %<br>%         |

| t <sub>CONVERT</sub>         | Conversion Time                 |                                                                                                                         |                  | 40               |                    | ms             |

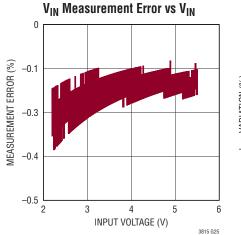

| Input Voltage Re             | adback                          |                                                                                                                         |                  |                  |                    | <u> </u>       |

| N                            | Resolution<br>LSB Step Size     |                                                                                                                         |                  | 13<br>4          |                    | Bits<br>mV     |

| V <sub>F/S</sub>             | Full Scale Input Voltage        | (Note 9)                                                                                                                |                  | 131              |                    | V              |

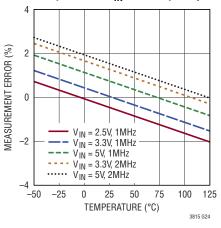

| V <sub>IN_TUE</sub>          | Total Unadjusted Error          |                                                                                                                         | •                |                  | ±1.5               | %              |

| t <sub>CONVERT</sub>         | Conversion Time                 |                                                                                                                         |                  | 40               |                    | ms             |

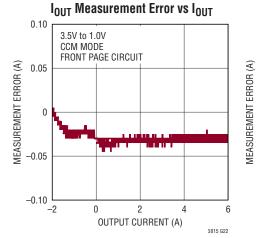

| Output Current R             | eadback                         |                                                                                                                         |                  |                  |                    |                |

| N                            | Resolution<br>LSB Step Size     |                                                                                                                         |                  | 13<br>10         |                    | Bits<br>mA     |

| V <sub>F/S</sub>             | Full Scale Output Current       |                                                                                                                         |                  | ±82              |                    | A              |

| I <sub>OUT_TUE</sub>         | Total Unadjusted Error          |                                                                                                                         |                  |                  | ±3                 | %              |

| t <sub>CONVERT</sub>         | Conversion Time                 |                                                                                                                         |                  | 40               |                    | ms             |

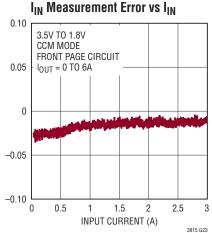

| Input Current Rea            | adback                          | · · · · · · · · · · · · · · · · · · ·                                                                                   |                  |                  |                    | <u> </u>       |

| N                            | Resolution<br>LSB Step Size     |                                                                                                                         |                  | 13<br>10         |                    | Bits<br>mA     |

| V <sub>F/S</sub>             | Full Scale Input Current        |                                                                                                                         |                  | ±82              |                    | A              |

| I <sub>IN_TUE</sub>          | Total Unadjusted Error          |                                                                                                                         |                  |                  | ±3                 | %              |

| t <sub>CONVERT</sub>         | Conversion Time                 |                                                                                                                         |                  | 40               |                    | ms             |

### ELECTRICAL CHARACTERISTICS The • denotes the specifications which apply over the specified operating

junction temperature range,  $V_{IN} = 3.3V$  unless otherwise noted. (Note 2)

| SYMBOL                    | PARAMETER                                      | CONDITIONS                           | MIN | ТҮР    | MAX   | UNITS      |

|---------------------------|------------------------------------------------|--------------------------------------|-----|--------|-------|------------|

| Temperature Re            | eadback                                        |                                      |     |        |       | 1          |

| N                         | Resolution<br>LSB Step Size                    |                                      |     | 9<br>1 |       | Bits<br>°C |

| V <sub>F/S</sub>          | Full Scale Temperature                         |                                      |     | ±256   |       | °C         |

| T <sub>TUE</sub>          | Total Unadjusted Error                         |                                      |     | ±3     |       | °C         |

| t <sub>CONVERT</sub>      | Conversion Time                                |                                      |     | 40     |       | ms         |

| PMBus Interfac            | e Parameters                                   |                                      | I   |        |       | <u>.</u>   |

| V <sub>IH,</sub> SDA, SCL | Input High Voltage                             |                                      | 2.1 |        |       | V          |

| V <sub>IL,</sub> SDA, SCL | Input Low Voltage                              |                                      |     |        | 0.8   | V          |

| I <sub>IH,</sub> SDA, SCL | Input Leakage Current                          | $0V \le V_{PIN} \le 5.5V$            | -5  |        | 5     | μA         |

| V <sub>OL, SDA</sub>      | Output Low Voltage (SDA)                       | I <sub>SDA</sub> = 3mA               |     |        | 0.4   | V          |

| V <sub>OL, ALERT</sub>    | Output Low Voltage (ALERT)                     | I <sub>ALERT</sub> = 1mA             |     |        | 0.4   | V          |

| f <sub>SCL</sub>          | Serial Bus Operating Frequency                 |                                      | 10  |        | 400   | kHz        |

| t <sub>BUF</sub>          | Bus Free Time Between Stop and Start Condition |                                      | 1.3 |        |       | μs         |

| t <sub>HD_SDA</sub>       | Hold Time After (Repeated) Start Condition     |                                      | 0.6 |        |       | μs         |

| t <sub>SU_SDA</sub>       | Repeated Start Condition Setup Time            |                                      | 0.6 |        |       | μs         |

| t <sub>SU_STO</sub>       | Stop Condition Setup Time                      |                                      | 0.6 |        |       | μs         |

| t <sub>HD_DAT(OUT)</sub>  | Data Hold Time                                 |                                      | 300 |        | 900   | ns         |

| t <sub>HD_DAT(IN)</sub>   | Input Data Hold Time                           |                                      | 0   |        |       | ns         |

| t <sub>SU_DAT</sub>       | Data Set-Up Time                               |                                      | 100 |        |       | ns         |

| t <sub>LOW</sub>          | Clock Low Period                               |                                      | 1.3 |        | 10000 | μs         |

| t <sub>HIGH</sub>         | Clock High Period                              |                                      | 0.6 |        |       | μs         |

| t <sub>TIMEOUT_SMB</sub>  | Stuck PMBus Timer                              | Measured from last PMBus start event |     | 30     |       | ms         |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LTC3815 is tested under pulsed load conditions such that  $T_J \approx T_A$ . The LTC3815E is guaranteed to meet specifications from 0°C to 85°C junction temperature. Specifications over the -40°C to 125°C operating junction temperature range are assured by design, characterization and correlation with statistical process controls. The LTC3815I is guaranteed over the -40°C to 125°C operating junction temperature range. Note that the maximum ambient temperature consistent with these specifications is determined by specific operating conditions in conjunction with board layout, the rated package thermal impedance and other environmental factors.

**Note 3:** The junction temperature  $(T_J, in °C)$  is calculated from the ambient temperature  $(T_A, in °C)$  and power dissipation (PD, in Watts) according to the formula:

$\mathsf{T}_\mathsf{J} = \mathsf{T}_\mathsf{A} + (\mathsf{PD} \bullet \theta_\mathsf{JA})$

where  $\theta_{\text{JA}}$  (in °C/W) is the package thermal impedance.

Note 4 : The dynamic input supply current is higher due to power MOSFET gate charging ( $Q_G \times f_{OSC}$ ). See applications Information for more information.

Note 5: The LTC3815 is tested in a feedback loop that servos  $V_{FB}$  to a referenced voltage with the  $I_{TH}$  pin forced to a voltage between 0.6V and 1V.

Note 6: Guaranteed by design, not subject to test.

**Note 7:** This IC includes overtemperature protection that is intended to protect the device during momentary overload conditions. Junction temperature will exceed 125°C when overtemperature protection is active. Continuous operation above the specified maximum junction temperature may impair device reliability or permanently damage the device.

**Note 8:** The LTC3815 uses valley current mode control so the current limits specified correspond to the valley of the inductor current waveform. Maximum load current is higher and equals the valley current limit  $I_{LIM}$  plus one half of the inductor ripple current.

Note 9: The maximum input and output voltage is 5.5V.

Note 10: Total output accuracy is the sum of the tolerances of I\_{REF,} R\_{REF(EXTERNAL)}, \Delta V\_{OUT,OFFSET}, and  $\Delta I_{REF,LINE} \bullet \Delta V_{IN}$ .

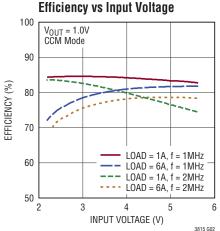

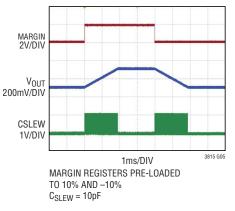

**Output Margining**

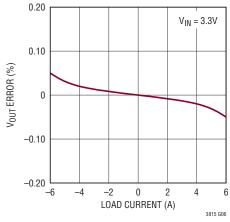

Load Regulation

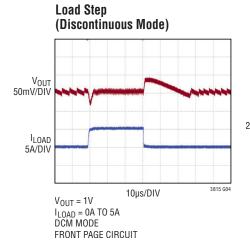

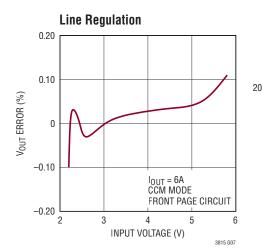

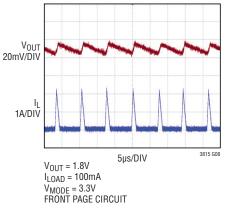

**Discontinuous Mode Operation**

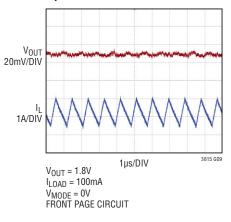

**Forced Continuous Mode** Operation

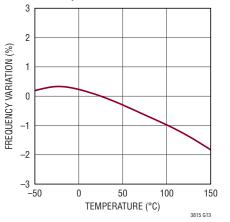

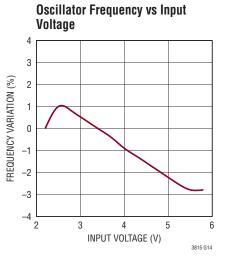

Oscillator Frequency vs Temperature

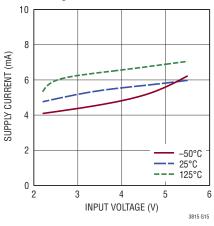

Quiescent Current vs Input Voltage

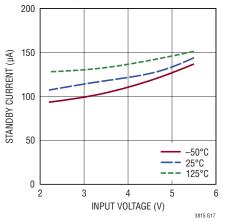

Standby Current vs Input Voltage

$I_{IN},\,I_{OUT}$  Measurement Error vs Temperature,  $V_{IN}$  and Frequency

LINEAR

Switch On-Resistance vs Input Voltage

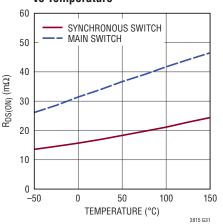

Switch On-Resistance vs Temperature

**Dynamic Supply Current**

vs Input Voltage

3

40

33

27

20

13

7

0

2

SUPPLY CURRENT (mA)

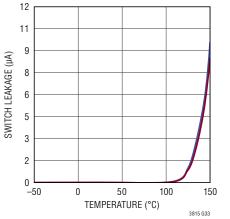

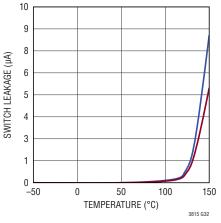

Switch Leakage vs Temperature, Main Switch

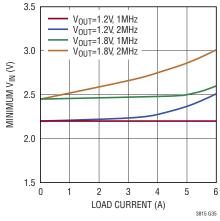

Minimum  $V_{\text{IN}}$  vs Load,  $V_{\text{OUT}}$  and Frequency

3815fa

4

INPUT VOLTAGE (v)

1MHz

2MHz

6

3815 G34

5

# PIN FUNCTIONS

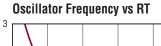

$R_T$  (Pin 1): Oscillator Frequency. This pin provides two modes of setting the constant switching frequency. Connect a resistor from  $R_T$  pin to ground to program the switching frequency from 400kHz to 3MHz. Tying this pin to  $V_{\rm IN}$  enables the internal 1MHz oscillator frequency.

**ASEL (Pin 2):** Serial Bus Address Configuration Input. Connect a  $\pm 1\%$  resistor from this pin to ground in order to select the 3 LSBs of the serial bus interface address. (see Table 5).

**MARGIN (Pin 3):** Fast Margining Select. In the default mode when this pin is floating, the reference voltage margin offset is changed with MFR\_VOUT\_COMMAND through the serial interface. If this pin is pulled high, the reference voltage margin offset is immediately ramped to the value pre-stored in the MFR\_VOUT\_MARGIN\_HIGH register. If this pin is pulled low, the reference voltage margin offset is immediately ramped to the value pre-stored in MFR\_VOUT\_MARGIN\_HIGH register.

**WP (Pin 4):** Write Protect Pin. Pulling this pin high disables writes to MFR\_VOUT\_COMMAND, MFR\_VOUT\_MARGIN\_HIGH, and MFR\_VOUT\_MARGIN\_LOW. When this pin is grounded, there are no write restrictions.

**ALERT** (Pin 5): Open Drain Digital Output. Connect the system SMBALERT interrupt signal to this pin. A pull-up resistor is required in the application.

**CLKOUT (Pin 6):** Clock Out Signal for 2-Phase Operation. The phase of this clock is  $180^{\circ}$  with respect to the internal clock. Signal swing is from V<sub>IN</sub> to GND.

**SDA (Pin 7):** Serial Bus Data Input and Output. A pull-up resistor is required in the application.

**SCL (Pin 8):** Serial Bus Clock Input. A pull-up resistor is required in the application.

**MODE/SYNC (Pin 9):** Mode Selection and External Clock Input. If this pin is tied to  $V_{IN}$ , discontinuous mode is enabled at light loads. If this pin is connected to ground, forced continuous mode is selected. Driving the MODE/ SYNC pin with an external clock signal will synchronize the switching frequency to the applied frequency. There is an internal 20k resistor to ground on this pin. **SW (Pins 10, 11, 13, 14, 18, 19, 21, 22, 23):** Switching Node. This pin connects to the drains of the internal main and synchronous power MOSFET switches.

**NC (Pins 12, 20):** No Connection. Can be connected to ground or left open. This pin does not connect to any internal circuitry.

$PV_{IN}$  (Pins 15-17): Power Input Supply.  $PV_{IN}$  connects to the source of the internal P-channel power MOSFET. This pin is independent of  $V_{IN}$  and may be connected to the same voltage or to a **lower** voltage supply.

**PGOOD (Pin 29):** Power Good. This open-drain output is pulled down to SGND on start-up and while the output voltage is outside the power good window set by the PGLIM pin. If the output voltage increases and stays inside the power good window for more than the delay programmed at the PGFD pin, the PGOOD pin is released. If the output voltage leaves the power good window for more than 16 switching cycles the PGOOD pin is pulled down.

$V_{IN}$  (Pin 24): Signal Input Supply. Decouple this pin to SGND with a capacitor. This pin powers the internal control circuitry. This pin is independent of PV<sub>IN</sub> and may be connected to the same voltage or to a **higher** supply voltage.

**PGFD (Pin 25):** PGOOD Deglitch Filter Delay Select. The voltage at this pin sets the delay that the output must be in regulation before the PGOOD flag is asserted. The delay can be programmed to one of seven discrete values where  $t_{DELAY} = 200\mu s \cdot 2^N$  (N = 0 to 5, 7).

**RUN\_MSTR (Pin 26):** Master Run. The power up threshold is set at 1V. When forced below 0.4V, all circuitry is shut off and the IC is put into a low current shutdown mode  $(I_Q < 1\mu A)$ .

**RUN\_STBY (Pin 27):** Standby Mode Off. The regulator power up threshold is set at 1V. When forced below 0.4V, only the voltage regulator is shut off while the ADC and PMBus interface are still active. When shut off, the ADC refresh rate is reduced to 1Hz and the IC quiescent current is reduced to 120 $\mu$ A. This pin sources 2.5 $\mu$ A. Do not pull up with a low impedance (<10k $\Omega$ ).

### PIN FUNCTIONS

$C_{SLEW}$  (Pin 28): Slew Rate Control. Add a capacitor to program the V<sub>OUT</sub> transition slew rate during margining. The slew rate is equal to 0.1% per ms per nF slew rate capacitance. With a 1nF capacitor, the slew rate is 0.1%/ms. Two default slew rates are also available when this pin is open or shorted to V<sub>IN</sub>.

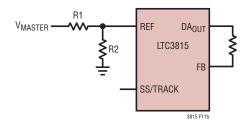

**TRACK/SS (Pin 30):** Tracking/Soft-Start Input. For softstart, a capacitor to ground at this pin sets the ramp rate of the output voltage (approximately  $5V/sec/\mu F$ ). For coincident tracking, connect this pin to a resistive divider between the voltage to be tracked and ground.

$V_{SS\_SENSE}$  (Pin 31):  $V_{OUT}$  Negative Terminal Voltage Sense. The internal unity gain differential gain amplifier connects to the  $V_{OUT}$  negative terminal through this pin. Tying this pin to the  $V_{IN}$  pin forces the IC to operate as a slave in a two-phase configuration.

$V_{CC\_SENSE}$  (Pin 32):  $V_{OUT}$  Positive Terminal Voltage Sense. The internal unity gain differential gain amplifier connects to the  $V_{OUT}$  positive terminal through this pin.

DA<sub>OUT</sub> (Pin 33): Differential Amplifier Output.

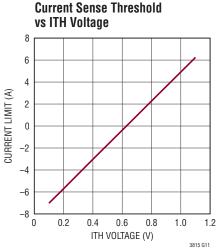

$I_{TH}$  (Pin 34): Error Amplifier Output and Switching Regulator Compensation Point. The current comparator's trip threshold is linearly proportional to this voltage. Use an RC network between the  $I_{TH}$  pin and the  $V_{FB}$  pin to compensate the feedback loop for optimum transient response.

**FB (Pin 35):** Error Amplifier Input. FB will be servoed to the REF pin voltage plus or minus any margining offset set through the serial interface.

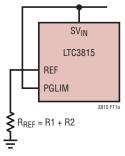

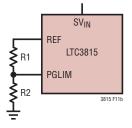

**REF (Pin 36):** Reference Input and Programming Pin. The voltage at this pin is the default reference that the output is regulated to. The PMBus interface allows margining around this default voltage by up to  $\pm 25\%$ . This pin can be driven by an external voltage or can be programmed with a resistor to ground. An internal accurate low drift 100µA current source times the external resistor sets the reference voltage.

**PGLIM (Pin 37):** PGOOD Threshold Programming Pin. The voltage difference  $\Delta V$  between this pin and SGND sets the V<sub>OUT</sub> overvoltage threshold to V<sub>REF</sub>+0.4 •  $\Delta V$  and the undervoltage threshold to V<sub>REF</sub>-0.4 •  $\Delta V$ . Tying this pin to V<sub>IN</sub> sets the threshold to its default value of ±10%.

**SGND (Pin 38):** Signal Ground. Reference setting resistor, slew rate control capacitor, and frequency setting resistor connections should return to SGND. For optimum load regulation, the SGND pin should be kelvin-connected to the PCB location between the negative terminals of the output capacitors and should not be connected through the PGND plane.

**PGND (Exposed Pad Pin 39):** Power Ground. Must be soldered to PCB for electrical connection and rated thermal performance.

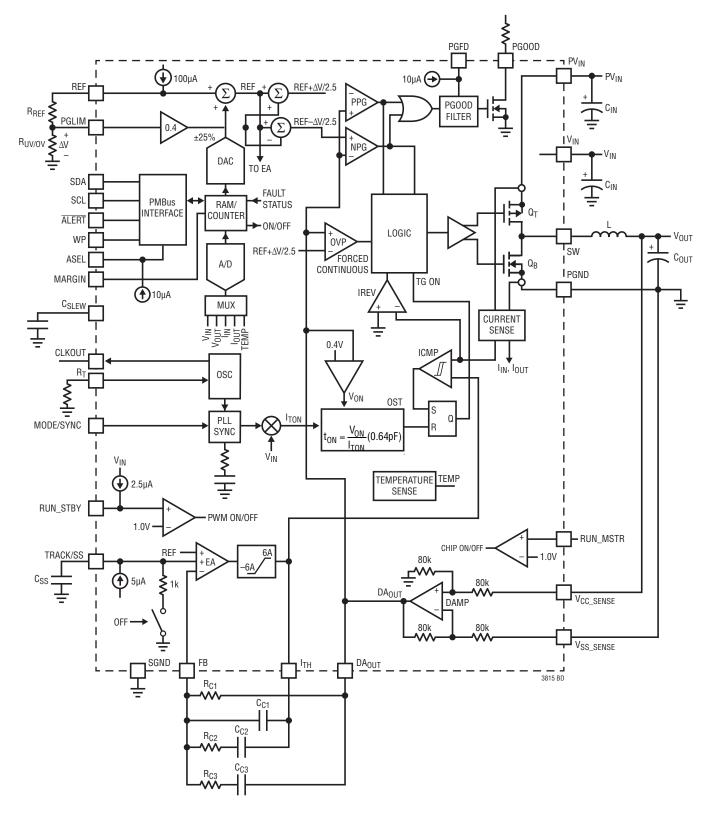

# **BLOCK DIAGRAM**

| Table 1. LTC3815 Supported PMBus Comma | nds |

|----------------------------------------|-----|

|----------------------------------------|-----|

| PMBUS<br>Command<br>Code | COMMAND NAME              | PMBUS-DEFINED SMBUS<br>TRANSACTION TYPE | SCALING   | DATA<br>BYTES | DESCRIPTION                                                                                                                                                                                                          |

|--------------------------|---------------------------|-----------------------------------------|-----------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x01                     | OPERATION                 | R/W Byte                                |           | 1             | On/Off Command and Set Output to MFR_VOUT_<br>MARGIN_HIGH or MFR_VOUT_MARGIN_LOW value                                                                                                                               |

| 0x20                     | VOUT_MODE                 | Read Byte                               |           | 1 or 2        | Read Data Format for MFR_VOUT_COMMAND<br>Hard-wired to VID format (0x3E), not writable                                                                                                                               |

| 0x79                     | STATUS_WORD               | R/W Word                                |           | 2             | Read Fault Status: Communication fault, PGOOD, $V_{IN}$ UV, $V_{OUT}$ OV, overtemperature, $V_{IN}$ fault, $V_{OUT}$ fault Individual faults are reset by writing a '1' to the bit position of the fault to be reset |

| 0x88                     | READ_VIN                  | R Word                                  | 4mV/Bit   | 2             | Read V <sub>IN</sub>                                                                                                                                                                                                 |

| 0x89                     | READ_IIN                  | R Word                                  | 10mA/Bit  | 2             | Read I <sub>IN</sub>                                                                                                                                                                                                 |

| 0x8B                     | READ_VOUT                 | R Word                                  | 0.5mV/Bit | 2             | Read V <sub>OUT</sub>                                                                                                                                                                                                |

| 0x8C                     | READ_IOUT                 | R Word                                  | 10mA/Bit  | 2             | Read I <sub>OUT</sub>                                                                                                                                                                                                |

| 0x8D                     | READ_TEMPERATURE_1        | R Word                                  | 1°C/Bit   | 2             | Read Die Temperature (°C)                                                                                                                                                                                            |

| 0X98                     | PMBUS_REVISION            | Read Byte                               |           | 1 or 2        | Read PMBus Revision = 0x22 for Rev 1.2                                                                                                                                                                               |

| 0xD7                     | MFR_IOUT_PEAK             | R/W Word                                | 10mA/Bit  | 2             | Read highest output current observed since last restart<br>Write will restart peak monitor routine                                                                                                                   |

| 0xDD                     | MFR_VOUT_PEAK             | R/W Word                                | 0.5mV/Bit | 2             | Read highest output voltage observed since last restart<br>Write will restart peak monitor routine                                                                                                                   |

| 0xDE                     | MFR_VIN_PEAK              | R/W Word                                | 4mV/Bit   | 2             | Read highest input voltage observed since last restart<br>Write will restart peak monitor routine                                                                                                                    |

| 0xDF                     | MFR_TEMPERATURE1_<br>PEAK | R/W Word                                | 1°C/Bit   | 2             | Read highest temperature observed since last restart<br>Write will restart peak monitor routine                                                                                                                      |

| 0xE1                     | MFR_IIN_PEAK              | R/W Word                                | 10mA/Bit  | 2             | Read highest input current observed since last restart<br>Write will restart peak monitor routine                                                                                                                    |

| 0xE3                     | MFR_CLEAR_PEAKS           | W Byte                                  |           | 0, 1 or 2     | Clear all peak values, write data is ignored                                                                                                                                                                         |

| 0xE5                     | MFR_VOUT_MARGIN_HIGH      | R/W Word                                | 0.1%/Bit  | 2             | Same format as MFR_VOUT_COMMAND                                                                                                                                                                                      |

| 0xE7                     | MFR_SPECIAL_ID            | R Word                                  |           | 2             | Read 16-bit value (0x8000) that GUI will recognize as LTC3815                                                                                                                                                        |

| 0xE8                     | MFR_VOUT_COMMAND          | R/W Word                                | 0.1%/Bit  | 2             | $V_{OUT}$ Margining Command $\pm 25\%$ range at 0.1%/bit in 2's compliment. Defaults to 0% at power-up                                                                                                               |

| 0xED                     | MFR_VOUT_MARGIN_LOW       | R/W Word                                | 0.1%/Bit  | 2             | Same format as MFR_VOUT_COMMAND                                                                                                                                                                                      |

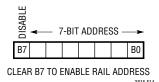

| 0xFA                     | MFR_RAIL_ADDRESS          | R/W Byte                                |           | 1 or 2        | Set Common PMBus Address (B6-B0), Clear B7 to<br>enable. Set B7 to disable. Valid addresses are 0x00 to<br>0x7F.                                                                                                     |

| 0xFD                     | MFR_RESET                 | W Byte                                  |           | 0, 1 or 2     | Reset PMBus Interface and ADC to Power-On State Write data is ignored                                                                                                                                                |

#### Main Control Loop

The LTC3815 is a 6A current mode monolithic step-down regulator with PMBus Interface. The accurate 100µA current source on the REF pin allows the user to use just one external resistor to program the output voltage. In normal operation, the internal top power MOSFET is turned on for a fixed interval determined by a one-shot timer, OST. When the top power MOSFET turns off, the bottom power MOSFET turns on until the current comparator, ICMP, trips, restarting the one-shot timer and initiating the next cycle. Inductor current is determined by sensing the voltage drop across the bottom power MOSFET's  $\mathsf{V}_{\mathsf{DS}}.$  The voltage on the I<sub>TH</sub> pin sets the comparator threshold corresponding to the inductor valley current. The error amplifier, EA, adjusts this  $I_{TH}$  voltage by comparing the feedback signal, V<sub>FB</sub>, from the output voltage with that of voltage on the REF pin. If the load current increases, it causes a drop in the feedback voltage relative to the internal reference. The I<sub>TH</sub> voltage then rises until the average inductor current matches that of the load current.

At low load current, the inductor current can drop to zero and become negative. This is detected by current reversal comparator, IREV, which then shuts off the bottom power MOSFET, resulting in discontinuous operation. Both power MOSFETs will remain off with the output capacitor supplying the load current until the I<sub>TH</sub> voltage rises above the zero current level (~0.6V) to initiate another cycle. Discontinuous mode operation is disabled by tying the MODE pin to V<sub>IN</sub>, which forces continuous synchronous operation regardless of output load.

The operating frequency is determined by the value of the  $R_T$  resistor, which programs the current for the internal oscillator. The internal phase-lock loop servos the switching regulator on-time to track the internal oscillator to force constant switching frequency. If an external clock signal is detected on the MODE/SYNC pin, the phase-lock loop will servo the on-time to track the external clock signal instead.

#### V<sub>OUT</sub> Margining

The LTC3815 has an internal 9-bit DAC that provides up to  $\pm 25\%$  adjustment at 0.1%/bit resolution around the reference voltage set at the REF pin. The digital offset value is changed with the MFR\_VOUT\_COMMAND command

through the PMBus interface. When a change in the reference is detected, the reference is ramped (0.1%/step) from its current value to the new value at a rate set by the capacitor value connected to the  $C_{SLEW}$  pin, thus providing programmable slew rate of the  $V_{OUT}$  transition. To eliminate the latency of the PMBus transaction when faster changes are required, the LTC3815 can be pre-loaded with two additional offsets with the MFR\_VOUT\_MARGIN\_HIGH and MFR\_VOUT\_MARGIN\_LOW commands. The reference offset can then be switched between any of these three register values with the 3-state MARGIN pin. When using the MARGIN pin, the latency of the V<sub>OUT</sub> transition is limited only by the chosen  $C_{SLEW}$  capacitor and the loop bandwidth of the power supply. Changes to these registers are prevented by pulling the write protect (WP) pin high.

#### **Telemetry Readback**

The LTC3815 has an integrated 13-bit ADC that monitors and performs conversions on the input and output voltage, input and output current, and die temperature. The values are refreshed at a 25Hz rate and are readable through the PMBus interface.

A peak monitor is also available for each of these telemetry measurements to provide that highest value measured since the start of the monitor. The monitor is reset by the MFR\_CLEAR\_PEAKS command, writing to the individual peak register, or de-asserting RUN\_MSTR.

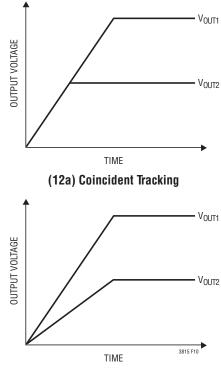

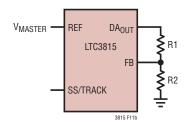

#### Output Voltage Tracking and Soft-Start

The LTC3815 allows the user to program its output voltage ramp rate by means of the TRACK/SS pin. An internal 5µA pulls up the TRACK/SS pin to  $V_{IN}$ . Putting an external capacitor on TRACK/SS enables soft starting the output to prevent current surge on the input supply. If no capacitor is connected or TRACK/SS pin is connected to  $V_{IN}$ , the ramp rate defaults to 1.1 volts/ms. For output tracking applications, TRACK/SS can be externally driven by another voltage source. For TRACK/SS less than the output voltage reference (set by the  $I_{REF}$  resistor and margin register), the TRACK/SS voltage will override the reference input to the error amplifier, thus regulating the feedback voltage to that of TRACK/SS pin. During this start-up time, the LTC3815 will operate in discontinuous mode. When TRACK/SS is

above the reference voltage, tracking is disabled and the feedback voltage will regulate to the reference voltage. Either concurrent or ratiometric tracking can be implemented by connecting the track voltage to either the  $I_{REF}$  pin or the TRACK/SS pin as described in the applications section.

#### **Output Power Good**

When the LTC3815's output voltage is within the its power good window of the regulation point, the output voltage is good and the PGOOD pin is pulled high with an external resistor. Otherwise, an internal open-drain pull-down device ( $40\Omega$ ) will pull the PGOOD pin low. This window is programmed by the PGLIM pin by connecting it to a resistive divider to the REF pin. This allows the the PGOOD window to be programmed as a percentage of the output voltage reference. If PGLIM is tied to V<sub>IN</sub>, the PGOOD window defaults to ±10%.

The PGOOD Filter Delay pin provides a user programmable delay from output voltage good to the rising edge of PGOOD. A wide range of delays from 200 $\mu$ s to 25ms can be user programmed by a configuration resistor connected to the PGFD pin. To prevent unwanted PGOOD glitches during transients or dynamic V<sub>OUT</sub> changes, the LTC3815's PGOOD falling edge includes a blanking delay of approximately 16 switching cycles.

Continuous operation is forced during OV and UV condition except during start-up when the TRACK/SS pin is ramping up to the internal reference voltage.

#### Master Shutdown and Standby Modes

There are three different ways to shut down the LTC3815: RUN\_MSTR pin, RUN\_STBY pin, and the ON bit of the OPERATION command.

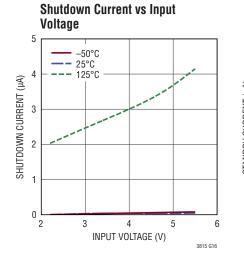

Pulling the RUN\_MSTR pin low forces the LTC3815 into a master shutdown state, turning off both power MOSFETs, the internal control circuitry, the ADC converter, and the PMBus interface. Also, all data written to the internal registers, such as the margin register, will be reset to the power-on state. Supply current in this mode is typically less than  $1\mu$ A.

Pulling RUN\_STBY pin low or clearing the ON bit in the OPERATION register puts the LTC3815 in a standby mode where the regulator is off but the ADC and PMBus are still active. In standby mode the LTC3815 will still respond to the PMBus host but will only refresh the telemetry data at 1Hz rate instead of 25Hz. In standby mode the supply current is 120 $\mu$ A. Exiting standy mode with the rising edge of the ON bit resets all faults and the ALERT pin. All data written to the internal registers, such as the margin registers, is not affected by this shutdown mode, so when RUN\_STBY is re-asserted, the V<sub>OUT</sub> will power back up to the last value written prior to shutdown (as long as no change to the margin registers or MARGIN pin was made during shutdown).

For the switcher to run and provide output regulation all three must be asserted, i.e. RUN\_MSTR and RUN\_STBY pins high and OPERATION ON bit set. At power on or master shutdown, the ON bit is automatically set in the OPERATION register. Pulling RUN\_MSTR low overrides the standby controls and puts the LTC3815 in master shutdown.

| INPU     | CONDITION | S      |                  | ON/OFF | STATES                    |       |

|----------|-----------|--------|------------------|--------|---------------------------|-------|

| RUN_MSTR | RUN_STBY  | ON BIT | V <sub>OUT</sub> | PMBus  | ADC                       | IQ    |

| High     | Х         | 0      | OFF              | ON     | 1Hz Refresh<br>(see Note) | 120µA |

| Low      | Х         | Х      | OFF              | OFF    | OFF                       | <1µA  |

| High     | High      | 1      | ON               | ON     | 25Hz<br>Refresh           | 5mA   |

| High     | Low       | Х      | OFF              | ON     | 1Hz Refresh<br>(see Note) | 120µA |

#### Table 2. Shutdown Modes

Note: Only  $V_{\text{IN}},\,V_{\text{OUT}}$  and temperature telemetry are refreshed.

#### **Short Circuit Protection**

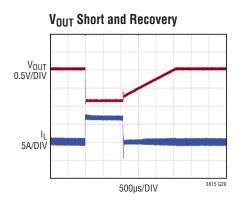

The LTC3815 has a precision cycle-by-cycle current limit to prevent inductor saturation in a short circuit condition. The valley of the inductor current is guaranteed to not exceed 6A ±10%. The maximum cycle-by-cycle inductor current is therefore limited to 6A + 10% +  $\Delta I_L$ , where  $\Delta I_L$  depends on the inductor valley and operating frequency but is typically ~2A. Internal control circuitry also guarantees smooth recovery with no output voltage overshoot once the short is removed.

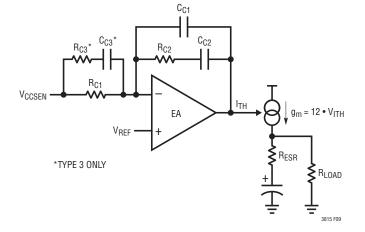

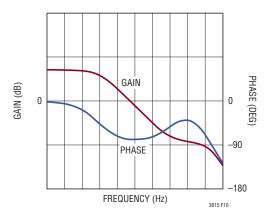

#### 25MHz Error Amplifier and Remote Sense Differential Amplifier

The LTC3815 utilizes a 25MHz error amplifier and differential amplifier for fast and accurate output voltage regulation. The operational amplifier style error amplifier allows precision tuning of the system poles and zeros for optimal transient response. The remote sense differential amplifier allows output voltage sensing at the point-of-load and thus provides very accurate regulation of the output voltage and telemetry readback regardless of load current. The sensed output voltage is available at the DA<sub>OUT</sub> pin (referenced to SGND). This pin is typically connected to the FB pin which is the error amplifier "-" input.

#### Using Separate VIN/PVIN Supplies

The LTC3815 has two supply pins:  $V_{IN}$  that supplies the IC control circuitry and  $PV_{IN}$  that supplies the driver and power switches.  $V_{IN}$  requires a minimum of 2.25V to guarantee proper operation, while  $PV_{IN}$  may be able to supply power to the load at lower voltages if the load demands do not exceed the weaker capability of the power switches at the lower voltage. To maximize the lower operating range of the supply voltage, two separate supplies can be used – a  $V_{IN}$  supply that is > 2.25V and rated at 10mA or higher and a  $PV_{IN}$  supply, rated for the load, that can be run all the way into dropout. Each supply pin has an individual undervoltage-lockout comparator to shut off the supply when its respective voltage is too low to guarantee proper operation.

#### Thermal Warning and Thermal Shutdown

The LTC3815 has two levels of thermal thresholds and two levels of responses. When the internal die temperature exceeds 150°C, the overtemperature bit in the STATUS\_WORD is set and the ALERT pin pulls low to alert the PMBus master. If the temperature continues to rise and exceeds 170°C, the LTC3815 shuts down all circuitry, including output regulation, and will no longer respond to the PMBus host. Both temperature monitors have about 20°C of hysteresis before the overtemperature condition is cleared. The temperature warning bit in the STATUS\_WORD is latched and remains set until the host clears it.

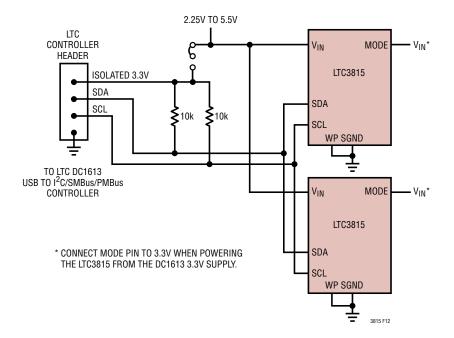

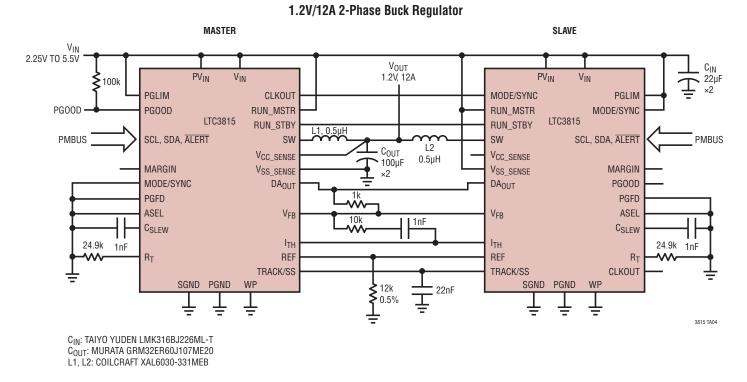

#### 2-Phase Operation

For output loads that demand more than 6A of current, two LTC3815's can be paralleled to run out-of-phase to provide up to 12A output current. To configure a 2-phase system, one LTC3815 will act as a master and the other a slave (see the schematic in the Typical Applications section). Connecting the V<sub>SS SENSE</sub> pin to V<sub>IN</sub> puts the LTC3815 in slave mode by tri-stating its error amplifier and remote sense amplifier. The I<sub>TH</sub> pins of both IC's are connected together so that both are regulating the inductor current based on the master's I<sub>TH</sub> voltage. The master's CLKOUT pin is a clock waveform that is 180° out-of-phase to its internal clock. This CLKOUT can be connected to the MODE/SYNC pin of the slave to force the slave's PLL to lock onto this clock input and run out-of-phase with the master. The RUN STBY pins are also connected together as a handshaking signal between the two so that both will shutoff together in case of a fault in only one of the phases, such as overtemperature condition.

See the Applications Information section for further details regarding 2-phase operation.

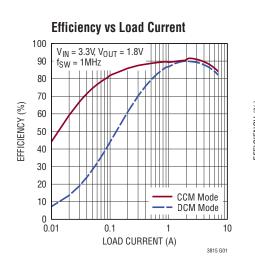

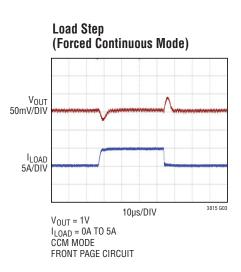

#### **Discontinuous/Forced Continuous Operation**

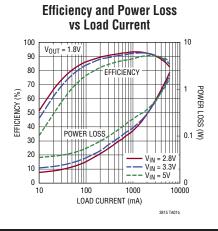

The LTC3815 can operate in one of two modes selectable with the MODE/SYNC pin: discontinuous mode or forced continuous mode. Connecting the MODE/SYNC pin to  $V_{IN}$  selects discontinuous mode. Discontinuous mode is selected when high efficiency at very light loads is desired. In this mode, when the inductor current reverses, the bottom MOSFET turns off to minimize the efficiency loss due to reverse current flow. This reduces the conduction loss and slightly improves the efficiency. As the load reduces, the driver switching frequency drops in proportion to the load, which further improves efficiency by minimizing gate charge losses.

Forcing the MODE/SYNC pin low enables forced continuous mode operation. In forced continuous mode, the bottom MOSFET is always on when the top MOSFET is off, allowing the inductor current to reverse at low currents. This mode is less efficient due to conduction and switching losses, but has the advantage of better transient response at low currents, constant frequency operation, and the ability to maintain regulation when sinking current.

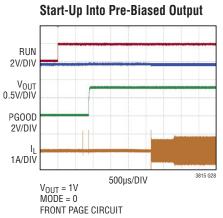

During soft-start, the LTC3815 forces the controller to operate in discontinuous mode until the soft-start voltage reaches the internal reference to guarantee smooth startup into a precharged output capacitor. During margining transitions and overvoltage conditions, however, the LTC3815 always operates in forced continuous mode to allow the switcher to sink current.

#### SERIAL INTERFACE

The LTC3815 serial interface is a PMBus compliant slave device and can operate at any frequency between 10kHz and 400kHz. The address is configurable using an external resistor. In addition the LTC3815 always responds to the global broadcast address of 0x5A or 0x5B (7 bit). The serial interface supports the following protocols defined in the PMBus specifications: 1) send command, 2) write byte, 3) write word, 4) group, 5) read byte and 6) read word. The PMBus write operations are not acted upon until a complete valid message is received by the LTC3815 including the STOP bit.

#### **Communication Failure**

Attempts to access unsupported commands or writing invalid data to supported commands will result in a CML fault. The CML bit is set in the STATUS\_WORD command and the ALERT pin is pulled low.

#### **Device Addressing**

The LTC3815 offers four different types of addressing over the PMBus interface, specifically: 1) global, 2) device, 3) rail addressing and 4) alert response address (ARA).

Global addressing provides a means of the PMBus master to address all LTC3815 devices on the bus. The LTC3815 global address is fixed 0x5A or 0x5B (7 bit) or 0xB4 or 0xB6 (8 bit) and cannot be disabled.

Device addressing provides the standard means of the PMBus master communicating with a single instance of an LTC3815. The value of the device address is set by the ASEL configuration pin. Rail addressing provides a means of the PMBus master addressing a set of channels connected to the same output rail, simultaneously. This is similar to global addressing, however, the PMBus address can be dynamically assigned by using the MFR\_RAIL\_ADDRESS command. It is recommended that rail addressing should be limited to command write operations.

All four means of PMBus addressing require the user to employ disciplined planning to avoid addressing conflicts.

#### Fault Status

The STATUS\_WORD and ALERT pin provide fault status information of the LTC3815 to the host.

#### **Bus Timeout Failure**

The LTC3815 implements a timeout feature to avoid hanging the serial interface. The data packet timer begins at the first START event before the device address write byte. Data packet information must be completed within 25ms or the LTC3815 will tri-state the bus and ignore the given data packet. Data packet information includes the device address byte write, command byte, repeat start event (if a read operation), device address byte read (if a read operation), and all data bytes.

The user is encouraged to use as high a clock rate as possible to maintain efficient data packet transfer between all devices sharing the serial bus interface. The LTC3815 supports the full PMBus frequency range from 10kHz to 400kHz.

# Similarity Between PMBus, SMBus and $\mathrm{I}^{2}\mathrm{C}$ 2-Wire Interface

The PMBus 2-wire interface is an incremental extension of the SMBus. SMBus is built upon  $I^2C$  with some minor differences in timing, DC parameters and protocol. The PMBus/SMBus protocols are more robust than simple  $I^2C$ byte commands because PMBus/SMBus provide time-outs to prevent bus hangs and optional packet error checking (PEC) to ensure data integrity. In general, a master device that can be configured for  $I^2C$  communication can be used for PMBus communication with little or no change to hardware or firmware. Repeat start (restart) is not supported by all  $I^2C$  controllers but is required for SMBus/ PMBus reads. If a general purpose  $I^2C$  controller is used, check that repeat start is supported.

For a description of the minor extensions and exceptions PMBus makes to SMBus, refer to PMBus Specification Part 1 Revision 1.1: Paragraph 5: Transport.

For a description of the differences between SMBus and  $I^2C$ , refer to System Management Bus (SMBus) Specification Version 2.0: Appendix B—Differences Between SMBus and  $I^2C$ .

#### **PMBus Serial Interface**

The LTC3815 communicates with a host (master) using the standard PMBus serial bus interface. The Timing Diagram, Figure 1, shows the timing relationship of the signals on the bus. The two bus lines, SDA and SCL, must be high when the bus is not in use. External pull-up resistors or current sources are required on these lines.

The LTC3815 is a slave device. The master can communicate with the LTC3815 using the following formats:

- Master transmitter, slave receiver

- Master receiver, slave transmitter

The following PMBus protocols are supported:

- Write Byte, Write Word, Send Byte

- Read Byte, Read Word

- Alert Response Address

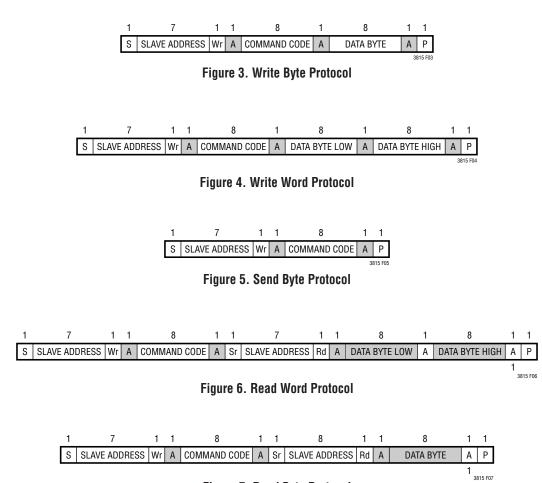

Figures 3 through 6 illustrate the aforementioned PMBus protocols. All transactions support GCP (group command protocol).

Figure 2 is a key to the protocol diagrams in this section.

#### Figure 1. Timing Diagram

| 1  | 7                            | 1         | 1    | 8                                              | 1     | 1       |

|----|------------------------------|-----------|------|------------------------------------------------|-------|---------|

| S  | SLAVE ADDRESS                | Wr        | А    | DATA BYTE                                      | Α     | Р       |

|    |                              |           | х    |                                                | Х     |         |

| S  | START CONDIT                 | ON        |      |                                                |       |         |

| Sr | REPEATED STA                 | RT C      | OND  | ITION                                          |       |         |

| Rd | READ (BIT VAL                | JE 0      | F 1) |                                                |       |         |

| Wr | WRITE (BIT VAL               | UE (      | OF 0 | )                                              |       |         |

| Х  | 01101111 011021              | • • • • • |      | INDICATES THAT THAT THAT THAT THAT THE VALUE C | ••••• |         |

| А  | ACKNOWLEDGE<br>FOR AN ACK OF |           |      | IT POSITION MAY<br>A NACK)                     | BE 0  |         |

| Ρ  | STOP CONDITION               | DN        |      |                                                |       |         |

| PE | C PACKET ERROF               |           | DE   |                                                |       |         |

|    | MASTER TO SL                 | AVE       |      |                                                |       |         |

|    | SLAVE TO MAS                 |           | PRO  | TOCOL                                          | 3     | 815 F02 |

|    |                              |           |      |                                                | 3     | 010102  |

Figure 2. PMBus Packet Protocol Diagram Element Key

A value shown below a field in the following figures is a mandatory value for that field.

The data formats implemented by PMBus are:

- Master transmitter transmits to slave receiver. The transfer direction in this case is not changed.

- Master reads slave immediately after the first byte. At the moment of the first acknowledgment (provided by the slave receiver) the master transmitter becomes a master receiver and the slave receiver becomes a slave transmitter.

- Combined format. During a change of direction within a transfer, the master repeats both a start condition and the slave address but with the R/W bit reversed. In this case, the master receiver terminates the transfer by generating a NACK on the last byte of the transfer and a STOP condition.

Examples of these formats are shown in Figures 3 through 7.

Figure 7. Read Byte Protocol

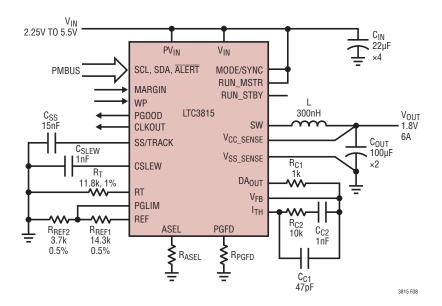

The basic LTC3815 application circuit is shown in Figure 8.

#### **Operating Frequency**

Selection of the operating frequency is a trade-off between efficiency and component size. High frequency operation allows the use of smaller inductor and capacitor values. Operation at lower frequencies improves efficiency by reducing internal gate charge losses but requires larger inductance values and/or capacitance to maintain low output ripple voltage. The operating frequency of the LTC3815 is determined by an external resistor that is connected between the RT pin and ground. The value of the resistor sets the ramp current that is used to charge and discharge an internal timing capacitor within the oscillator and can be calculated by using the following equation:

$$\mathsf{R}_{\mathsf{T}} = \frac{1.15 \bullet 10^{11}}{\left(\mathsf{f}_{\mathsf{OSC}}\right)^{1.11}} \Omega$$

Frequencies as high as 3MHz are possible, as long as the minimum on-time requirement is met (see next section).

Tying the RT pin to  $V_{IN}$  sets the default internal operating frequency to 1MHz  $\pm 15\%.$

The LTC3815's internal oscillator can be synchronized to an external frequency by applying a square wave clock signal to the MODE/SYNC pin. During synchronization, the top switch turn-on is locked to the rising edge of the external frequency source. The synchronization frequency range is 300kHz to 3MHz. During synchronization, discontinuous operation is disabled.

The internal PLL has a synchronization range of  $\pm 30\%$  around its programmed frequency. Therefore, during external clock synchronization be sure that the external clock frequency is within this  $\pm 30\%$  range of the R<sub>T</sub> programmed frequency.

When using the RT pin to program the oscillator frequency, a square wave clock that is running 180° out-of-phase with the internal oscillator is available at the CLKOUT pin for connection to a second LTC3815 for 2-phase operation (see the 2-Phase section).

Figure 8. 1.8V, 6A Step-Down Regulator

#### Minimum Off-Time and Minimum On-Time Considerations

The minimum off-time,  $t_{OFF(MIN)}$ , is the smallest amount of time that the LTC3815 is capable of turning on the bottom power MOSFET, tripping the current comparator and turning the power MOSFET back off. This time is generally about 100ns. The minimum off-time limit imposes a maximum duty cycle of  $t_{ON}/(t_{ON} + t_{OFF(MIN)})$ . If the maximum duty cycle is reached, due to a dropping input voltage for example, then the output will drop out of regulation. The minimum input voltage to avoid dropout is:

$$V_{\text{IN(MIN)}} = V_{\text{OUT}} \bullet \frac{t_{\text{ON}} + t_{\text{OFF(MIN)}}}{t_{\text{ON}}}$$

Conversely, the minimum on-time is the smallest duration of time in which the top power MOSFET can be in its "on" state. This time is typically 75ns. In continuous mode operation, the minimum on-time limit imposes a minimum duty cycle of:

$$DC_{MIN} = f \bullet t_{ON(MIN)}$$

where  $t_{ON(MIN)}$  is the minimum on-time. As the equation shows, reducing the operating frequency will alleviate the minimum duty cycle constraint.

In the cases where the minimum duty cycle is surpassed, the output voltage will still remain in regulation, but the switching frequency will decrease from its programmed value. This is an acceptable result in many applications, so this constraint may not be of critical importance in most cases. High switching frequencies may be used in the design without any fear of severe consequences. As the sections on inductor and capacitor selection show, high switching frequencies allow the use of smaller board components, thus reducing the size of the application circuit.

#### Inductor Selection

Given the desired input and output voltages, the inductor value and operating frequency determine the ripple current:

$$\Delta I_{L} = \frac{V_{OUT}}{f \bullet L} \bullet \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

Lower ripple current reduces core losses in the inductor, ESR losses in the output capacitors and output voltage ripple. Highest efficiency operation is obtained at low frequency with small ripple current. However, achieving this requires a large inductor. There is a trade-off between component size, efficiency and operating frequency.

A reasonable starting point is to choose a ripple current that is about 30-40% of  $I_{OUT(MAX)}$ . This is especially important at low  $V_{OUT}$  operation where  $V_{OUT}$  is 1.8V or below. Care must be given to choose an inductance value that will generate a big enough current ripple so that the chip's valley current comparator has enough signal-to-noise ratio to force constant switching frequency. Meanwhile, also note that the largest ripple current does not exceed a specified maximum, the inductance should be chosen according to:

$$L = \frac{V_{OUT}}{f \bullet \Delta I_{L(MAX)}} \bullet \left(1 - \frac{V_{OUT}}{V_{IN(MAX)}}\right)$$

Once the value for L is known, the type of inductor must be selected. Actual core loss is independent of core size for a fixed inductor value, but is very dependent on the inductance selected. As the inductance or frequency increases, core losses decrease. Unfortunately, increased inductance requires more turns of wire and therefore copper losses will increase.

Ferrite designs have very low core losses and are preferred at high switching frequencies, so design goals can concentrate on copper loss and preventing saturation. Ferrite core material saturates "hard", which means that LTC3815 inductance collapses abruptly when the peak design current is exceeded. This results in an abrupt increase in inductor ripple current and consequent output voltage ripple. Do not allow the core to saturate!

Different core materials and shapes will change the size/ current and price/current relationship of an inductor. Toroid or shielded pot cores in ferrite or permalloy materials are small and don't radiate much energy, but generally cost more than powdered iron core inductors with similar characteristics. The choice of which style inductor to use

mainly depends on the price versus size requirements and any radiated field/EMI requirements. New designs for surface mount inductors are available from Toko, Vishay, NEC/Tokin, Cooper, TDK, Würth Elektronik and Coilcraft. Refer to Table 3 for more details.

| INDUCTANCE<br>(µH) | DCR<br>(mΩ) | MAX<br>CURRENT (A) | DIMENSIONS<br>(mm) | HEIGHT<br>(mm) |

|--------------------|-------------|--------------------|--------------------|----------------|