## **Switching Charger for 1-Cell Li-ion Batteries**

#### **ISL9220B**

The ISL9220B is a cost-effective and versatile battery charger for 1-cell Li-Polymer based portable applications.

The device features synchronous PWM technology, maximizing power efficiency, thus minimizing charge time and heat. The 1.2MHz switching frequency allows use of small external inductors and capacitors.

A simple charge current programming method is provided. External resistors program the fast charge and end-of-charge currents.

The two status outputs can be used to drive LEDs, or can be connected to the host processor.

A programmable charge timer provides the ability to detect defective batteries, and provides a secondary method of detecting charge termination.

A thermistor interface is provided for battery presence detection, and for temperature qualified charging conditions.

1

Additional features include preconditioning of an over-discharged battery, automatic recharge, and thermally enhanced QFN package.

## **Applications**

- PDAs and Smart Phones

- MP3 and Portable Media Players

- · Handheld GPS Devices

- Digital Still Cameras

- Industrial Handheld Scanners

#### **Features**

- Highly Integrated Battery Charger IC

- Charges 1 Li-ion or Li-Polymer Batteries

- Up to 2A Charge Current

- Synchronous Buck Topology, with Integrated Power FFTs

- 1.2MHz Switching Frequency

- 0.5% Charge Voltage Accuracy

- Input Current Limit Programmable with One External Resistor

- Thermistor Interface for Battery Detection and Temperature Qualified Charging

- Two Status Outputs

- Programmable Charge Safety Timer

- Short-Circuit and Thermal Protection

- Small 4x4mm TQFN Package

- -40°C to +85°C Operating Temperature Range

#### **Related Literature**

- Technical Brief <u>TB363</u> "Guidelines for Handling and Processing Moisture Sensitive Surface Mount Devices (SMDs)"

- Technical Brief <u>TB379</u> "Thermal Characterization of Packaged Semiconductor Devices"

- Technical Brief <u>TB389</u> "PCB Land Pattern Design and Surface Mount Guidelines for QFN Packages"

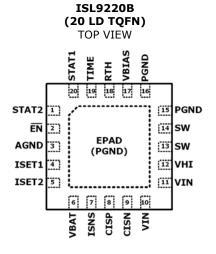

## **Pin Configuration**

## **Pin Descriptions**

| PIN#   | PIN<br>NAME | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                 |

|--------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | STAT2       | Open-drain indication pin. In conjunction with STAT1 this pin provides a unique indication for each charging state of the cycle. This pin is capable to sink 10mA minimum current to drive an LED.                                                                                                                                                                          |

| 2      | ĒN          | IC enable input. Drive this pin to logic LO to enable the charger. Drive this pin to logic HI to disable the charger. Do not leave this pin floating.                                                                                                                                                                                                                       |

| 3      | AGND        | Analog ground.                                                                                                                                                                                                                                                                                                                                                              |

| 4      | ISET1       | Charge current programing pin. Connect a resistor between this pin and the GND pin to set the charge current.                                                                                                                                                                                                                                                               |

| 5      | ISET2       | End-of-charge current programing pin. Connect a resistor between this pin and the GND pin to set the end-of-charge current.                                                                                                                                                                                                                                                 |

| 6      | VBAT        | Battery connection pin. Connect this pin to the battery. A $10\mu F$ or larger X5R ceramic capacitor is recommended for decoupling and stability purposes.                                                                                                                                                                                                                  |

| 7      | ISNS        | Output current sense pin. Connect a current sense resistor from this pin to VBAT. No decoupling capacitor is needed at this pin.                                                                                                                                                                                                                                            |

| 8      | CISP        | Input current sense positive connection pin. Connector a sense resistor from this pin the CISN.                                                                                                                                                                                                                                                                             |

| 9      | CISN        | Input current sense negative connection pin. Connector a sense resistor from this pin the CISP.                                                                                                                                                                                                                                                                             |

| 10, 11 | VIN         | Input supply voltage. Connect a 4.7µF ceramic capacitor from VIN to PGND.                                                                                                                                                                                                                                                                                                   |

| 12     | VHI         | High side NMOS FET gate drive supply pin. Connect a Schottky diode from VBIAS to this pin, and a $0.1\mu F$ capacitor to AGND, as shown in the "Typical Application" diagram on page 6.                                                                                                                                                                                     |

| 13, 14 | SW          | Switch node and inductor connection pin.                                                                                                                                                                                                                                                                                                                                    |

| 15, 16 | PGND        | Power ground.                                                                                                                                                                                                                                                                                                                                                               |

| 17     | VBIAS       | Internal 5V regulator output. Connect a 1µF ceramic capacitor from this pin to AGND.                                                                                                                                                                                                                                                                                        |

| 18     | RTH         | Input for an external NTC thermistor for battery temperature monitoring.                                                                                                                                                                                                                                                                                                    |

| 19     | TIME        | The TIME pin sets the oscillation period by connecting a timing capacitor between this pin and GND. The oscillator also provides a time reference for the charger. The timer function can be disabled by connecting the TIME pin to GND. If the timer is disabled, there will be no timeout function for any operation mode including trickle charge and fast charge modes. |

| 20     | STAT1       | Open-drain indication pin. In conjunction with STAT2 this pin provides a unique indication for each charging state of the cycle. This pin is capable to sink 10mA minimum current to drive an LED.                                                                                                                                                                          |

|        | PD          | Exposed pad. Connect to GND electrically. Thermally, connect as much as possible copper to this pad either on the component layer or other layers through thermal vias to enhance the thermal performance.                                                                                                                                                                  |

## **Ordering Information**

| PART<br>NUMBER<br>(Notes 1, 2, 3) | PART<br>MARKING | TEMPERATURE<br>RANGE (°C) | PACKAGE<br>Tape & Reel<br>(Pb-Free) | PKG.<br>DWG. # |

|-----------------------------------|-----------------|---------------------------|-------------------------------------|----------------|

| ISL9220BIRTZ-T                    | 922 OBIRTZ      | -40 to +85                | 20 Ld 4x4 TQFN                      | L20.4x4E       |

#### NOTES:

- 1. Please refer to TB347 for details on reel specifications.

- 2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 3. For Moisture Sensitivity Level (MSL), please see device information page for <u>ISL9220B</u>. For more information on MSL please see techbrief <u>TB363</u>.

FN7652.1 July 2, 2010

#### **Absolute Maximum Ratings**

#### **Thermal Information**

| Thermal Resistance (Typical)      | $\theta_{JA}$ (°C/W) | $\theta_{JC}$ (°C/W) |

|-----------------------------------|----------------------|----------------------|

| 4x4 QFN Package (Notes 4, 5)      | 40                   | 4.3                  |

| Maximum Junction Temperature (Pla | stic Package)        | +150°C               |

| Maximum Storage Temperature Range | ge65°                | °C to +150°C         |

| Pb-free reflow profile            |                      | ee link below        |

| http://www.intersil.com/pbfree/Pb | o-FreeReflow         | .asp                 |

#### **Recommended Operating Conditions**

| Ambient Temperature Range   | <br>-40°C to +85°C |

|-----------------------------|--------------------|

| Supply Voltage, VIN         | <br>4.5V to 14V    |

| Programmable Charge Current | <br>200mA to 2A    |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 4. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 5.  $\theta_{JC}$ , "case temperature" location is at the center of the exposed metal pad on the package underside.

# **Electrical Specifications** Typical specifications are measured at the following conditions: $T_A = +25$ °C; $V_{VIN} = 5V$ .

| PARAMETER                                                                            | SYMBOL               | TEST CONDITIONS                                                                                                                                             | MIN<br>(Note 6) | TYP  | MAX<br>(Note 6) | UNITS |

|--------------------------------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|-----------------|-------|

| POWER-ON RESET                                                                       |                      |                                                                                                                                                             |                 |      |                 | '     |

| Rising VIN Threshold                                                                 | V <sub>POR_R</sub>   |                                                                                                                                                             | 3.4             | 3.6  | 3.8             | V     |

| Falling VIN Threshold                                                                | V <sub>POR_F</sub>   |                                                                                                                                                             | 2.2             | 2.4  | 2.6             | V     |

| VIN-VBAT OFFSET VOLTAGE                                                              |                      |                                                                                                                                                             |                 |      |                 |       |

| Rising Offset Threshold                                                              | V <sub>OS_R</sub>    |                                                                                                                                                             | -               | 95   | 150             | mV    |

| Falling Offset Threshold                                                             | V <sub>OS_F</sub>    |                                                                                                                                                             | 10              | 65   | -               | mV    |

| SUPPLY CURRENT                                                                       |                      |                                                                                                                                                             |                 |      |                 |       |

| VIN Pin Supply Current                                                               | I <sub>CC(VIN)</sub> | (Note 7) PGOOD = TRUE, $\overline{EN} = L$                                                                                                                  | -               | 10   | 15              | mA    |

|                                                                                      | 33(11.1)             | PGOOD = TRUE, EN = H<br>VIN = 5V to 12V                                                                                                                     | -               | -    | 0.5             | mA    |

| Battery Discharge Current<br>(Total of currents flowing into VBAT,<br>ISNS, SW pins) | I <sub>DIS</sub>     | $V_{IN}$ < VPOR or $\overline{EN}$ = H 2V < $V_{BAT}$ < 11V                                                                                                 | -               | 2    | 5               | μA    |

| OVERVOLTAGE PROTECTION                                                               |                      |                                                                                                                                                             |                 |      |                 |       |

| Input OVP Rising Threshold                                                           | V <sub>IN_OVPR</sub> |                                                                                                                                                             | 14.5            | 15.0 | 15.5            | V     |

| Input OVP Falling Threshold                                                          | V <sub>IN_OVPF</sub> |                                                                                                                                                             | 14.0            | 14.5 | 15.0            | V     |

| OUTPUT CURRENT                                                                       |                      |                                                                                                                                                             |                 |      |                 |       |

| Fast Charge Current Accuracy                                                         | I <sub>CHG</sub>     | $\begin{array}{l} \text{RSNS} = 0.039\Omega \\ \text{RISET1} = 49.9 \text{k}\Omega \text{ (Nominal} \\ \text{I}_{\text{OUT}} = 1000 \text{mA)} \end{array}$ | -10             | -    | 10              | %     |

| Charge Termination Current Accuracy                                                  | I <sub>MIN</sub>     | $R_{SNS} = 0.039\Omega$<br>$R_{ISET2} = 300k\Omega$ (Nominal<br>$I_{MIN} = 100mA$ )                                                                         | -35             | -    | 35              | %     |

| Charge Termination Detection<br>Deglitch Time                                        |                      |                                                                                                                                                             | -               | 12   | -               | ms    |

FN7652.1 July 2, 2010

### **ISL9220B**

# **Electrical Specifications** Typical specifications are measured at the following conditions: $T_A = +25$ °C; $V_{VIN} = 5V$ . (Continued)

| PARAMETER                                                     | SYMBOL                    | TEST CONDITIONS                                       | MIN<br>(Note 6) | TYP | MAX<br>(Note 6) | UNITS |

|---------------------------------------------------------------|---------------------------|-------------------------------------------------------|-----------------|-----|-----------------|-------|

| Pre-Charge Current Range (Linear<br>Mode)                     | I <sub>PCHG</sub>         | V <sub>BAT</sub> < V <sub>PCHG</sub>                  | 25              | 50  | 90              | mA    |

| Pre-Charge Threshold Voltage                                  | V <sub>PCHG</sub>         |                                                       | 2.42            | 2.5 | 2.56            | V     |

| RECHARGE THRESHOLD                                            | I.                        |                                                       |                 |     | 1               |       |

| Recharge Voltage Threshold                                    | V <sub>RECHG</sub>        |                                                       | 3.85            | 4.0 | 4.1             | V     |

| TEMPERATURE MONITORING                                        | I.                        |                                                       |                 |     | 1               |       |

| High Battery Temperature Threshold                            | V <sub>TMIN</sub>         | Specified as % of V <sub>BIAS</sub>                   | 30              | 35  | 40              | %     |

| Low Battery Temperature Threshold                             | V <sub>TMAX</sub>         | Specified as % of V <sub>BIAS</sub>                   | 70              | 75  | 80              | %     |

| Battery Removal Threshold                                     | V <sub>RMV</sub>          | Specified as % of V <sub>BIAS</sub>                   | 90              | 95  | -               | %     |

| Thermistor Disable Threshold                                  | V <sub>T_DIS</sub>        |                                                       | -               | 250 | -               | mV    |

| Temperature Threshold Hysteresis                              | V <sub>T,HYS</sub>        |                                                       | -               | 180 | -               | mV    |

| Temperature Detection Deglitch Time                           |                           |                                                       | -               | 12  | -               | ms    |

| THERMAL PROTECTION                                            | I                         |                                                       |                 |     | П               |       |

| Thermal Shutdown Threshold                                    | T <sub>FD</sub>           |                                                       | -               | 140 | -               | °C    |

| Thermal Hysteresis                                            | T <sub>HYS</sub>          |                                                       | -               | 30  | -               | °C    |

| V <sub>BIAS</sub> OUTPUT                                      |                           |                                                       |                 |     |                 |       |

| Output Voltage                                                | V <sub>BIAS</sub>         | 5.3 < V <sub>IN</sub> < 15V, IV <sub>BIAS</sub> = 5mA | 4.70            | 5.0 | 5.25            | V     |

| Output Current                                                | I <sub>BIAS</sub>         | 5.3 < V <sub>IN</sub> < 15V                           | -               | -   | 5               | mA    |

| OSCILLATOR                                                    |                           |                                                       |                 |     |                 |       |

| Oscillation Period                                            | T <sub>OSC</sub>          | C <sub>TIME</sub> = 15nF                              | -               | 3.0 | -               | ms    |

| SWITCHING CHARGER AC CHARAC                                   | CTERISTICS                |                                                       |                 |     |                 |       |

| Switching Frequency                                           | Fosc                      |                                                       | 1.02            | 1.2 | 1.38            | MHz   |

| Maximum Duty Cycle                                            | D <sub>MAX</sub>          |                                                       | -               | 96  | -               | %     |

| Minimum Duty Cycle                                            |                           |                                                       | -               | 0   | -               | %     |

| Cycle-By-Cycle Current Limit                                  | I <sub>LIM</sub>          |                                                       | -               | 3.0 | -               | Α     |

| SWITCHING CHARGER DC CHARA                                    | CTERISTICS                |                                                       |                 |     |                 |       |

| High-Side MOSFET ON-resistance                                | r <sub>DS(ON)</sub> , HS1 |                                                       | -               | 112 | -               | mΩ    |

| Combined High-Side ON-resistance (Note 8)                     | r <sub>DS(ON)</sub> , HS2 | Measured between VIN and SW pins                      | -               | 224 | 450             | mΩ    |

| Low Side MOSFET ON-resistance                                 | r <sub>DS(ON)</sub> , L   |                                                       | -               | 72  | 180             | mΩ    |

| High-Side Path Reverse Leakage<br>Current                     | I <sub>REV</sub>          | V <sub>IN</sub> = 0V, VSW = 15V                       | -               | 1.0 | 5.0             | μA    |

| Charger Output Voltage                                        | V <sub>CHG</sub>          | I <sub>OUT</sub> = 100mA, T <sub>A</sub> = +25°C      | 4.179           | 4.2 | 4.221           | V     |

|                                                               |                           | I <sub>OUT</sub> = 100mA                              | 4.158           | 4.2 | 4.242           | V     |

| INPUT CURRENT SENSE AMPLIFIE                                  | R                         | 1                                                     | 1               |     | 1               | 1     |

| Input Bias Current at CSIP and CSIN,<br>Pin (Charger Enabled) | I <sub>ISIP_ON</sub>      | $\overline{EN} = L$                                   | -               | 100 | 200             | μА    |

| Input Current Limit Threshold                                 | I <sub>IN_LIM</sub>       | CSIP-CSIN                                             | 88              | 100 | 112             | mV    |

#### **ISL9220B**

# **Electrical Specifications** Typical specifications are measured at the following conditions: $T_A = +25$ °C; $V_{VIN} = 5V$ . (Continued)

| PARAMETER                                             | SYMBOL                | TEST CONDITIONS     | MIN<br>(Note 6) | TYP        | MAX<br>(Note 6) | UNITS |

|-------------------------------------------------------|-----------------------|---------------------|-----------------|------------|-----------------|-------|

| OUTPUT CURRENT SENSE AMPLIF                           | IER                   |                     |                 |            |                 |       |

| Input Bias Current at ISNS Pin,<br>(Charger Enabled)  | I <sub>ISNS_ON</sub>  | ĒN = L              | -               | 100        | 200             | μA    |

| Input Bias Current at ISNS Pin,<br>(Charger Disabled) | I <sub>ISNS_OFF</sub> | ĒN = H              | -               | -          | 1               | μА    |

| Input Bias Current at VBAT Pin,<br>(Charger Enabled)  | I <sub>VBAT_ON</sub>  | $\overline{EN} = L$ | -               | 75         | 100             | μA    |

| Input Bias Current at VBAT Pin,<br>(Charger Disabled) | I <sub>VBAT_OFF</sub> | ĒN = H              | -               | -          | 1               | μА    |

| LOGIC INPUT AND OUTPUTS                               |                       |                     |                 |            |                 |       |

| EN Pin Logic High                                     |                       |                     | 1.3             | <b>-</b> . | -               | V     |

| EN Pin Logic Low                                      |                       |                     | -               | <b>-</b> . | 0.4             | V     |

| STAT1, STAT2 Sink Current when ON                     |                       | Pin Voltage = 0.4V  | 10              |            | -               | mA    |

| STAT1, STAT2 Leakage Current when OFF                 |                       | Pin Voltage = 4.2V  | -               | -          | 1               | μА    |

#### NOTES:

- 6. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

- 7. PGOOD is defined as when  $V_{IN}$  and  $V_{BAT}$  meet all these conditions: 1.  $V_{IN} > V_{POR}$ , 2.  $V_{IN} V_{BAT} > V_{OS}$ , 3.  $V_{IN} < V_{INOVP}$ .

- 8. Limits should be considered typical and are not production tested.

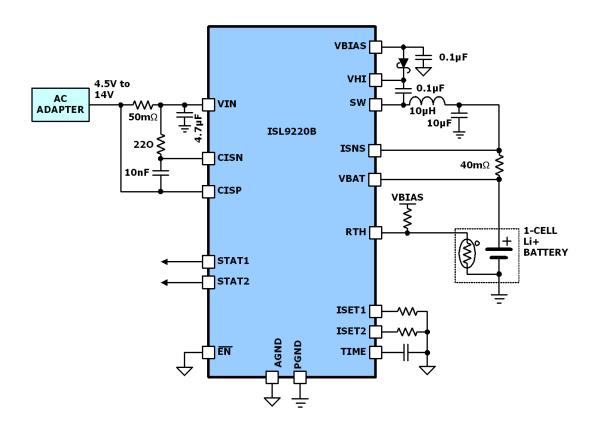

# **Typical Application**

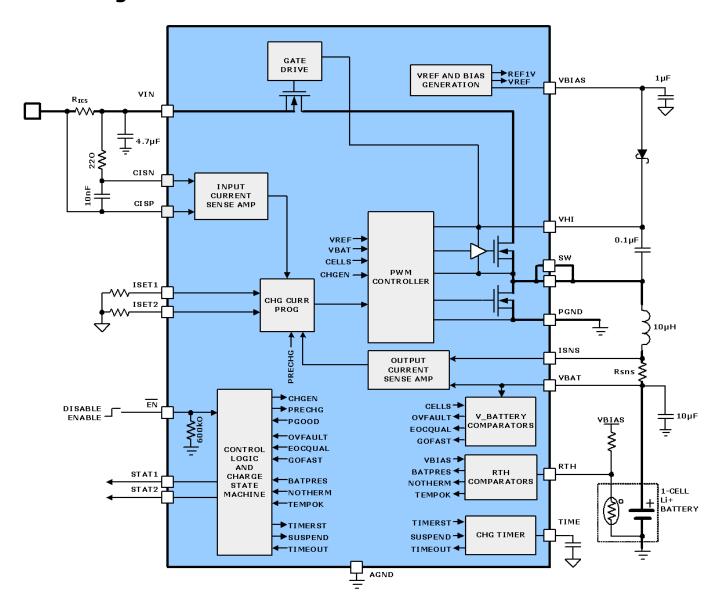

# **Block Diagram**

## **Theory of Operation**

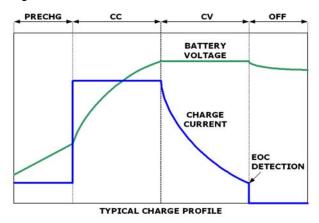

The ISL9220B is an integrated charger optimized for charging 1-cell Li-ion or Li-polymer batteries. It charges a battery with the constant current (CC) and constant voltage (CV) profile. The typical charge profile is shown in Figure 1.

FIGURE 1. TYPICAL CHARGE PROFILE

#### **POR and Power-Good**

The ISL9220, ISL9220A resets itself when  $V_{IN}$  undergoes transition from below  $V_{POR}$  to above  $V_{POR}$  threshold.

The ISL9220B has an internal PGOOD signal. Charging is prohibited if PGOOD is not true. See Note 7 on page 5 of the "Electrical Specifications" table for the definition of PGOOD.

#### **Valid Charge Temperatures**

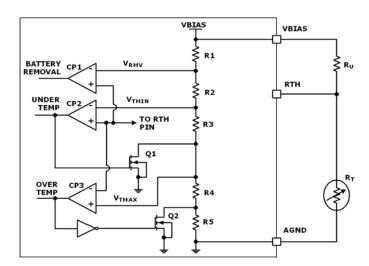

An external NTC thermistor can be used to provide temperature-qualified charging. The  $V_{BIAS}$  supply is used as a reference for the internal comparators. Thus, it is important that the  $V_{BIAS}$  supply also be used to bias the external voltage divider comprised of one or more fixed resistors and the thermistor. This scheme allows for the use of a wide variety of thermistors. The  $R_{TH}$  comparator block monitors the RTH pin voltage to determine if the battery temperature is within safe charging limits.

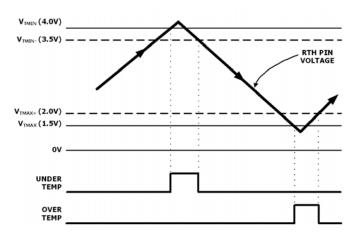

The ISL9220B uses two comparators (CP2 and CP3) to form a window comparator, as shown in Figure 2. When the NTC pin voltage is "out of the window", determined by the  $V_{TMIN}$  and  $V_{TMAX}$ , the ISL9220B stops charging and indicates a suspend condition. When the temperature returns to the set range, the charger resumes charging. The two MOSFETs, Q1 and Q2, produce hysteresis for both upper and lower thresholds. The temperature window is shown in Figure 3 for a 0°C to +50°C typical application using an industry standard type 103AT thermistor.

The temperature qualification function can be disabled by connecting the RTH pin to ground.

FIGURE 2. THERMISTOR INTERNAL CIRCUIT

FIGURE 3. THRESHOLD VOLTAGES FOR 0°C to +50°C WINDOW ( $V_{BIAS} = 5.0V$ )

#### **Battery Detection**

The presence or absence of the external thermistor is used to detect a battery.

When  $V_{RTH}$  is greater than  $V_{RTH,PRES}$ , i.e. when RTH pin is <u>not</u> connected to ground, battery detection is provided by the  $R_{TH}$  comparator block, as shown in Figure 2. With no battery connected, the RTH pin is pulled to  $V_{BIAS}$  by  $R_{U}$ , and thus  $V_{RTH}$  will exceed the  $V_{RTH,(NOBAT)}$  threshold. The internal battery presence signal is deglitched with a 12ms deglitcher, to avoid false indication of battery insertion or removal due to contact bounce or other noise.

#### **Battery Precharge**

When the charger is first enabled and no fault conditions are detected, if the battery connecting to the charger is deeply discharged, the charger will charge the battery in a reduced current for the battery to recover

intersil

If the battery voltage is less than the pre-charge voltage  $(V_{PCHG})$ , the charger operates in LDO mode, with an output current fixed at 50mA typical. In this mode, the output voltage can go to 0V. This provides the ability to recover a battery that has entered a safety-circuit undervoltage fault mode.

$$I_{PCHG} = 50 mA (EQ. 1)$$

When the cell voltage exceeds the pre-charge voltage threshold ( $V_{PCHG}$ ), fast charging will commence. If this threshold is not reached within the precharge timer period, a TIME-OUT-FAULT condition is asserted, and the charger is disabled.

#### **Charge Safety Timer**

An internal oscillator establishes a timing reference. The oscillation period is programmable with an external capacitor at the TIME pin,  $C_{Time}$ , as shown in the "Typical Application" diagram on page 6. The oscillator charges the timing capacitor to 1.5V and then discharges it to 0.5V in one period, both with  $10\mu A$  current. The period  $t_{OSC}$  is:

$$t_{OSC} = 0.2 \times 10^6 \times C_{Time}$$

(Sec) (EQ. 2)

Where C<sub>Time</sub> is in F.

A 1nF capacitor provides 0.2ms oscillation period. The allowable range of  $C_{\text{Time}}$  value is 100pF to 1µF, providing a programmable charge safety-timeout range of about 1.4 minutes to almost 10 days.

Total charge time, excluding any time required for precharge, is limited to a length of TIMEOUT. This can be calculated using Equation 3:

$$TIMEOUT = 2^{22} \times T_{OSC}$$

(Sec) (EQ. 3)

Total charge time for battery precharge is limited to a length of 1/8 TIMEOUT. This can be calculated using Equation 4:

$$TIMEOUT(PCHG) = 2^{19} \times T_{OSC}$$

(Sec) (EQ. 4)

The TIME pin can be grounded to disable the safety timer functions if not needed.

#### **Fast Charge**

The fast charge current is programmed by the resistor between the ISET1 pin and ground, and by the value of the  $R_{\mbox{\footnotesize{SNS}}}$  resistor.

$$I_{CHG} = \frac{1946}{R_{ISET1} \times R_{SNS}}$$

(mA) (EQ. 5)

Where  $R_{\mbox{\scriptsize ISET1}}$  is in  $k\Omega$  and  $R_{\mbox{\scriptsize SNS}}$  is in  $\Omega.$

For best accuracy, select  $R_{SNS}$  value that provides between 40mV to 80mV differential voltage across  $R_{SNS}$  at the desired maximum peak current (DC plus ripple).

#### **Charge Termination**

Output current is continuously monitored during charge. When current falls below the taper current threshold, charging will stop, and BATFUL is asserted to indicate a

9

successful charge completion. This taper current threshold is programmed by a single external resistor between ISET2 and ground.

$$I_{EOC} = \frac{1170}{R_{ISET2} \times R_{SNS}}$$

(mA) (EQ. 6)

Where  $R_{ISET2}$  is in  $k\Omega$  and  $R_{SNS}$  is in  $\Omega$ .

A secondary charge termination method is provided via the safety timer. The timeout period of this timer is programmable via a single external capacitor between the TIME pin and ground.

To disable the charge safety timer, tie the TIME pin to ground.

#### **Charge Current Sensing**

Charge current is sensed with an external current sense resistor. A low-inductance, precision resistor should be used for best performance.

#### **Input Current Sensing**

Input current is sensed with an external sense resistor. A low-inductance, precision resistor should be used for accurate input current limit.

An internal amplifier compares the voltage between CSIP and CSIN, and limits the current when this differential voltage exceeds the threshold voltage. The effective input current limit threshold is thus set by the value of the  $R_{ICS}$  resistor as calculated by Equation 7.

$$I_{IN(LIM)} = \frac{0.1}{R_{ICS}}$$

(A)

Where  $R_{ICS}$  is in  $\Omega$ .

The ISL9220, ISL9220A limits the battery charge current when the input current limit threshold is exceeded. This allows the most efficient use of AC-adapter power without overloading the adapter output.

A low pass filter is suggested to eliminate the switching noise, as shown in "Typical Application" on page 6.

## **Status Outputs**

**TABLE 1. STAT1 AND STAT2 TRUE TABLE**

| STAT1 | STAT2 | CHARGING CONDITION                    |

|-------|-------|---------------------------------------|

| L     | L     | Precharge, or fast charge in progress |

| L     | Н     | Charge Complete                       |

| Н     | L     | Fault                                 |

| Н     | Н     | Suspend                               |

STAT1 and STAT2 are configured to indicate various charging conditions as given in Table 1.

A fault status is triggered under one of these conditions:

- 1.  $V_{BAT} > V_{OUT}$  OVP threshold

- 2. Timeout occurs before the EOC current has been reached

July 2, 2010

To exit the fault mode, the input power has to be removed and re-applied, or the  $\overline{\text{EN}}$  pin is toggled to HI and back to LO.

## **Applications Information**

#### Power-on Reset (POR)

The ISL9220B resets itself as the input voltage rises above the POR rising threshold. The internal oscillator starts to oscillate, the internal timer is reset, and the charger begins to charge the battery. The STAT1/2 pins will indicate the operating condition according to Table 1.

#### **Trickle Charge**

If the battery voltage is below the trickle charge threshold, the ISL9220B charger delivers a small current to trickle charge the battery until the voltage reaches the fast charge threshold value. When  $V_{BAT}$  is below  $V_{PCHG}$ , the ISL9220B operates as a linear regulator, providing a 50mA constant current to output. When  $V_{BAT}$  reaches  $V_{PCHG}$ , the ISL9220B starts to operate as a switching charger and delivers the programmed fast charge current.

#### **Charge Cycle**

A charge cycle consists of three charge modes: trickle mode, constant current (CC) mode, and constant voltage (CV) mode. The charge cycle always starts with the trickle mode until the battery voltage stays above V<sub>PCHG</sub> (2.5V typical). If the battery voltage stays below V<sub>PCHG</sub>, the charger stays in the trickle mode. The charger moves to the CC mode after the battery voltage is above V<sub>PCHG</sub>. As the battery-pack terminal voltage rises to the final charge voltage, the CV mode begins. Since the battery terminal voltage is regulated at the constant output voltage in the CV mode, the charge current is expected to decline as the cell voltage rises. After the charge current drops below the end-of-charge level, which also programmable by R<sub>ISET2</sub>, the ISL9220B indicates the end-of-charge (EOC) with STAT1 and STAT2 and terminates the charge. The following events initiate a new charge cycle:

- POR

- A new battery being inserted (detected by RTH pin)

- Recovery from an battery over-temperature fault

- The EN pin is toggled from HI to LO

#### Recharge

After a charge cycle completes at a timeout event, charging is prohibited until the recharge condition ( $V_{\rm BAT}$  <  $V_{\rm RECHG}$ ) is met. Then the charging restarts with the timer reset to zero.

#### **Inductor and Output Capacitor Selection**

To achieve better steady state and transient response, ISL9220B typically uses a  $10\mu$ H inductor. The peak-to-peak inductor current ripple can be expressed in Equation 8:

$$\Delta I = \frac{V_{BAT} \cdot \left(1 - \frac{V_{BAT}}{V_{IN}}\right)}{L \cdot f_{S}}$$

(EQ. 8)

In Equation 8, usually the typical values can be used but to have a more conservative estimation, the inductance should consider the value with the worst case tolerance; and for switching frequency  $f_S$ , the minimum  $f_S$  from the "Electrical Specifications" table on page 4 can be used. A worst case for the charge current ripple is when the battery voltage is half of the input voltage.

To select the inductor, its saturation current rating should be at least higher than the sum of the maximum output current and half of the delta calculated from Equation 8. Another more conservative approach is to select the inductor with the current rating higher than the peak current limit.

Another consideration is the inductor DC resistance since it directly affects the efficiency of the converter. Ideally, the inductor with the lower DC resistance should be considered to achieve higher efficiency.

Inductor specifications could be different from different manufacturers so please check with each manufacturer if additional information is needed.

For the output capacitor, a ceramic capacitor can be used because of the low ESR values, which helps to minimize the output voltage ripple. A typical value of  $10\mu\text{F}/10\text{V}$  ceramic capacitor should be enough for most of the applications and the capacitor should be X5R or X7R.

#### **Board Layout Recommendations**

The ISL9220B is a high frequency switching charger and hence the PCB layout is a very important design practice to ensure a satisfactory performance.

The power loop is composed of the output inductor L, the output capacitor  $C_{OUT}$ , the SW pin and the PGND pin. It is important to make the power loop as small as possible and the connecting traces among them should be direct, short and wide; the same practice should be applied to the connection of the VIN pin, the input capacitor  $C_{IN}$  and PGND.

The switching node of the converter, the SW pin, and the traces connected to this node are very noisy, so keep the voltage feedback trace and other noise sensitive traces away from these noisy traces.

The input capacitor should be placed as close as possible to the VIN pin. The ground of the input and output capacitors should be connected as close as possible as well. In addition, a solid ground plane is helpful for a good EMI performance.

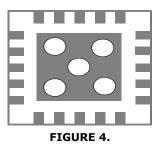

The ISL9220B employs a thermal enhanced QFN package with an exposed pad. In order to maximize the current capability, it is very important that the exposed pad under the package be properly soldered to the board

and also be connected to other layers through thermal vias. More thermal vias and more copper attached to the exposed pad usually result in better thermal performance. The exposed pad is big enough for 5 vias, as shown in Figure 4.

#### **Charging Flow Chart**

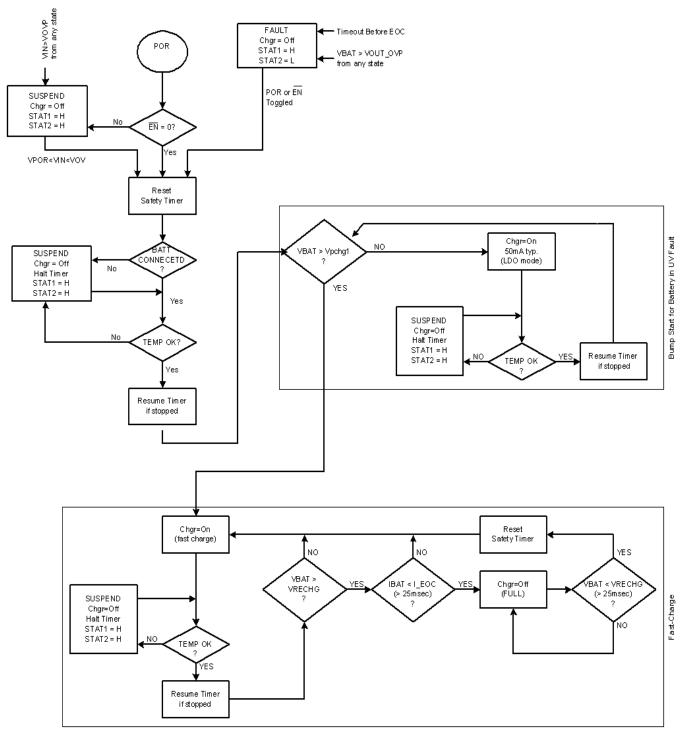

The charging flow chart is shown in Figure 5. The charging starts with trickle charge current, the ISL9220B charges the battery in 50mA. If  $V_{BAT}$  reaches  $V_{PCHG}$  before the trickle charge timeout interval, the operation will move to the CC mode. When the output voltage reaches the 4.2V final voltage, the operation will move to CV mode, where the battery is charged at a constant voltage. If the end-of-charge current is reached before the timeout interval is elapsed, the operation moves to charge complete state. The charging is terminated. After the termination, if the output voltage drops below the recharge threshold, a recharge starts and the timer is reset to zero.

In the event that the timeout condition is reached before the EOC condition is reached, the fault mode is entered. The fault mode can also be triggered by a  $V_{BAT}$  OVP event. To exit the fault mode, the input power has to be removed and re-applied, or the  $\overline{\text{EN}}$  pin is toggled to HI and back to LO, then a new cycle starts.

FIGURE 5. CHARGING FLOW CHART

# **Typical Operating Conditions**

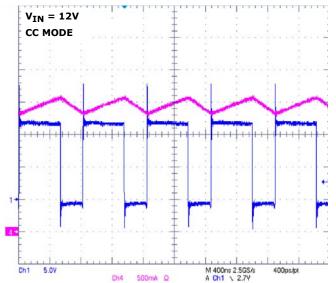

FIGURE 6. PWM WAVEFORM, CH1 = SW (5V/DIV); CH4 = INDUCTOR CURRENT (500mA/DIV)

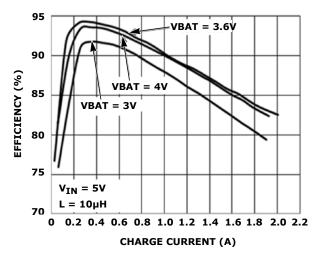

FIGURE 7. EFFICIENCY vs LOAD

### **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to web to make sure you have the latest Rev.

| DATE    | REVISION | CHANGE                                                                                                                                                      |

|---------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7/1/10  | FN7652.1 | Changed minimum limit for "IPCHG" on page 4 from 30 to 25mA. On page 4, changed "Minimum On-Time" with typical 20ns to "Minimum Duty Cycle" w/typical of 0% |

| 6/30/10 | FN7652.0 | Initial release.                                                                                                                                            |

#### **Products**

Intersil Corporation is a leader in the design and manufacture of high-performance analog semiconductors. The Company's products address some of the industry's fastest growing markets, such as, flat panel displays, cell phones, handheld products, and notebooks. Intersil's product families address power management and analog signal processing functions. Go to <a href="https://www.intersil.com/products">www.intersil.com/products</a> for a complete list of Intersil product families.

\*For a complete listing of Applications, Related Documentation and Related Parts, please see the respective device information page on intersil.com: <a href="ISL9220B">ISL9220B</a>

To report errors or suggestions for this datasheet, please go to www.intersil.com/askourstaff

FITs are available from our website at <a href="http://rel.intersil.com/reports/search.php">http://rel.intersil.com/reports/search.php</a>

For additional products, see <a href="https://www.intersil.com/product\_tree">www.intersil.com/product\_tree</a>

Intersil products are manufactured, assembled and tested utilizing ISO9000 quality systems as noted in the quality certifications found at <a href="https://www.intersil.com/design/quality">www.intersil.com/design/quality</a>

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

FN7652.1 July 2, 2010

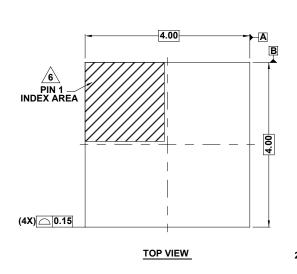

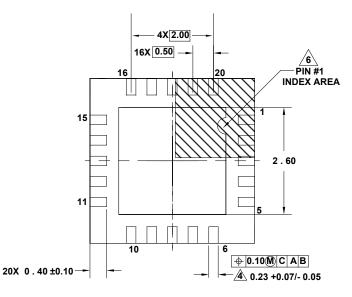

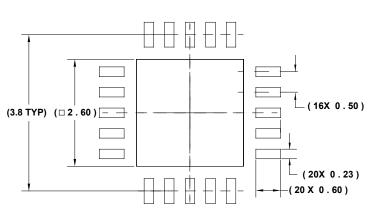

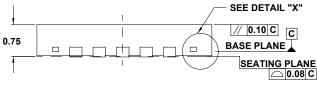

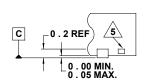

### **Package Outline Drawing**

#### L20.4x4E

20 LEAD THIN QUAD FLAT NO-LEAD PLASTIC PACKAGE Rev 0, 4/10

#### **BOTTOM VIEW**

15

SIDE VIEW

#### NOTES:

DETAIL "X"

- Dimensions are in millimeters.

Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to ASME Y14.5m-1994.

- 3. Unless otherwise specified, tolerance : Decimal  $\pm 0.05$

- <u>4.</u> Dimension applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- 5. Tiebar shown (if present) is a non-functional feature.

- The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.

- 7. JEDEC reference drawing: MO-229.

intersil